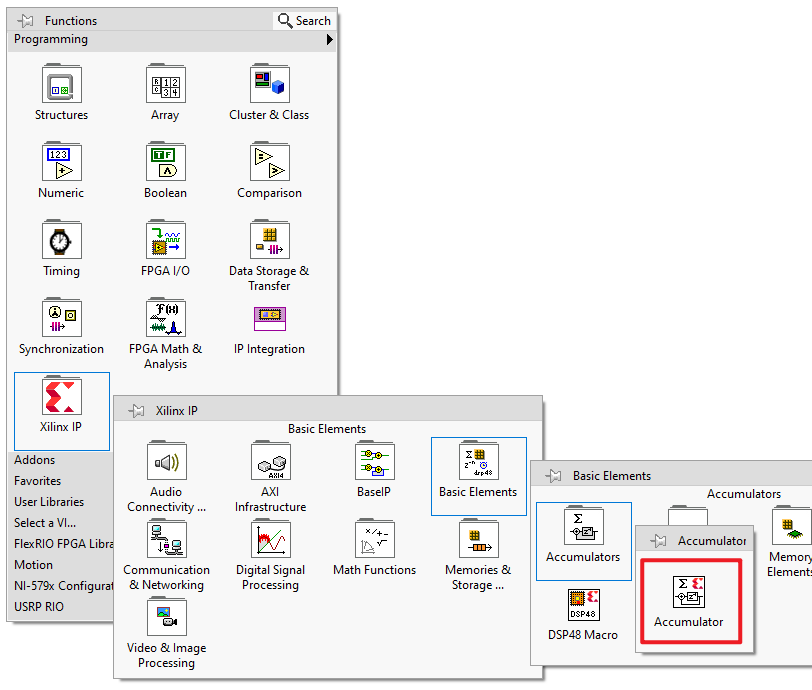

1. IP位于:

Functions/Programming/Xilinx IP/Basic Elements/Accumulators/Accumulator (如下图)

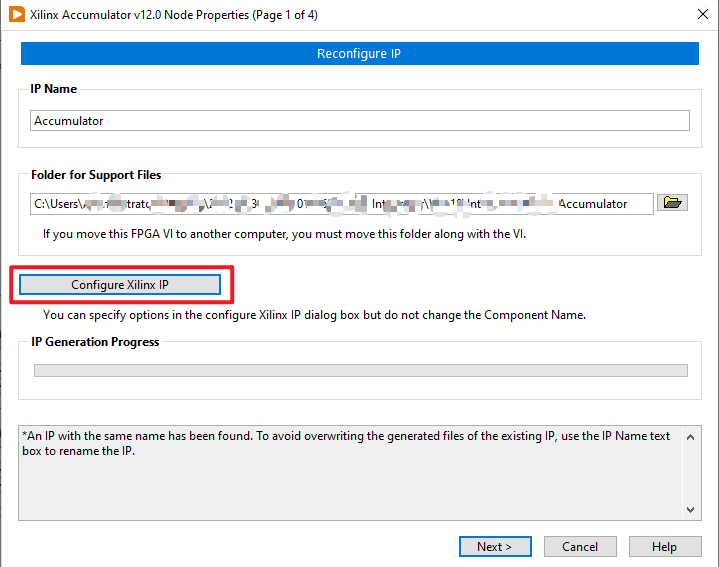

2. 双击原来的IP节点,打开它的LabVIEW配置窗口。

3. 单击

Configure Xilinx IP 按钮以打开 Vivado 自定义 IP 窗口。

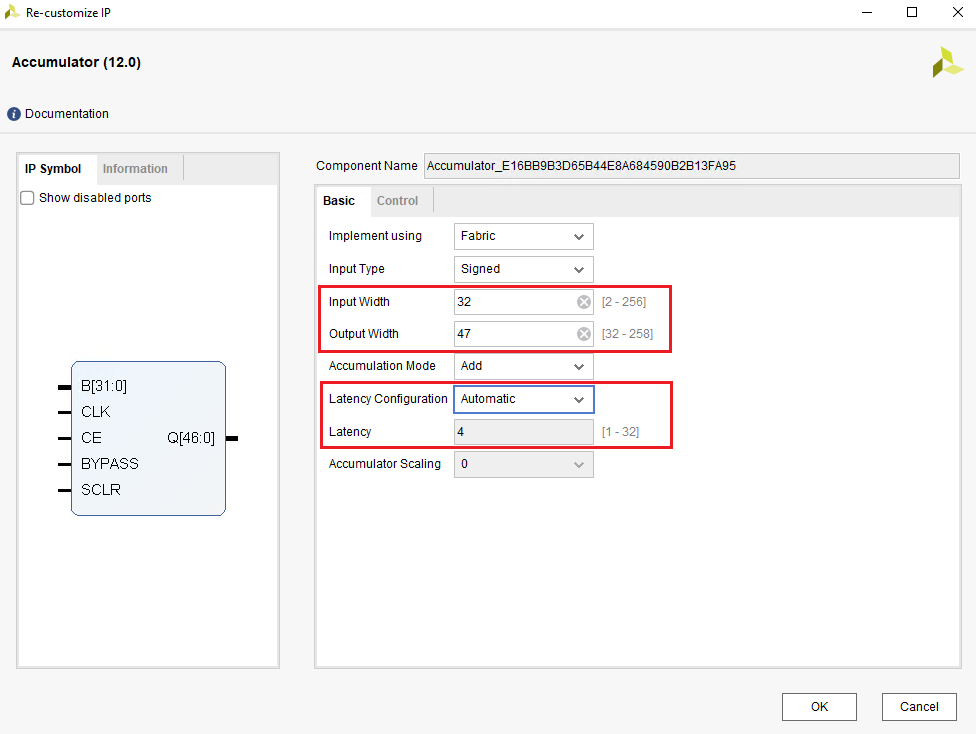

a. 根据您的需要设置输入宽度

Input Width;

b. 根据需要设置输出宽度

Output Width;

c. 配置延迟

Latency,如果您选择延迟为

自动 Automatic,您可以看到 Vivado 为您计算实际延迟,显示在

Latency 显示控件中。

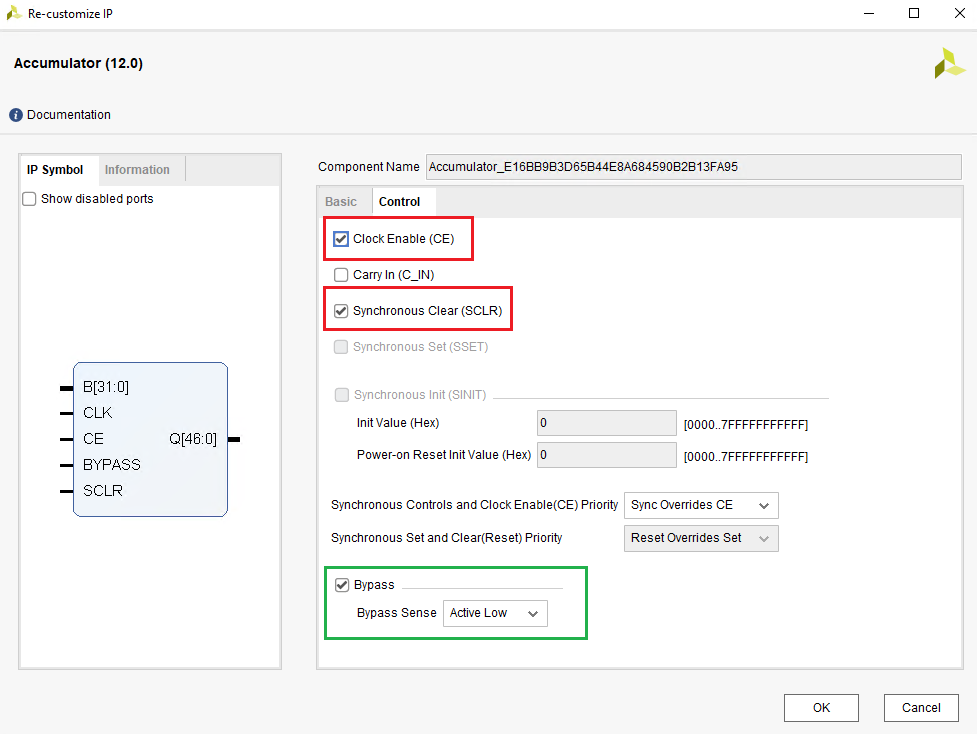

4. 勾选

Clock Enable(CE) ,这是让 IP 使用源时钟的使能输入端口。这个端口很关键,因为在 FPGA 中,并不是每个时钟周期都能准备好有效数据的。您可以将 FIFO 的

输出有效 Output valid 布尔值连接到 IP 的

CE 输入端口,可以很好地控制 IP 的行为。

5. 勾选

Synchronous Clear (SCLR) ,这是一个复位输入端口,用于 IP 清除当前寄存器的值并设置回

0 。如果您想要自定义初始值,可以使用

Synchronous Init (SINIT) 。

6.

可选设置:启用

旁路 Bypass 并为此输入选择

低电平有效/高电平有效 Active Low/Active High。

如果

Bypass 处于 Active 有效状态,则 IP 将其接收到的输入 (B) 直接传递到输出 (Q)。

如果

Bypass 处于 Inactive 无效状态,则 IP 执行累加工作,并输出(Q)累加结果。

7. 单击 OK,Vivado 将为您生成 IP。

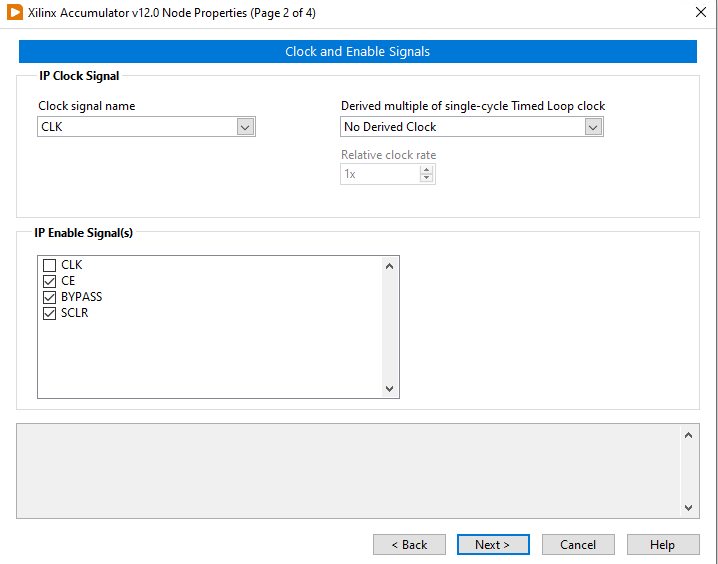

8. IP 生成工作完成后,点击 next 配置 IP 的 LabVIEW 接口。

a. 启用时钟信号,以及您需要的其他 IP 启用信号。例如:CE,Bypass,SCLR。

b. 单击下一步,进入 IP 端口配置页面。

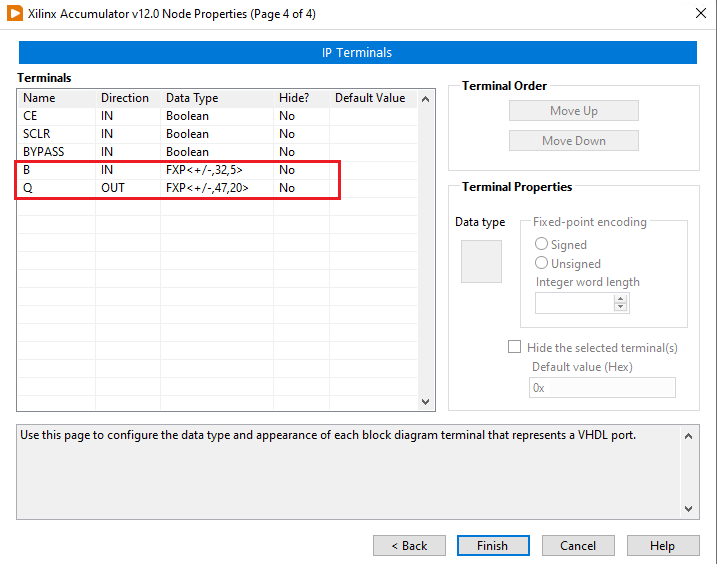

在这里,您需要在 LabVIEW 中定义 IP 端子接口的数据类型。

请确保 B & Q 的数据类型FXP的

总长度与您在 Vivado 中设置的相同(第 3 步),并设置

整数位长度 Integer word Length 。

如果您想保持输入和输出的精度相同,只需让

Length -

Integer word Length相等即可。例如(下图中的 32-5 = 47-20)

9. 单击

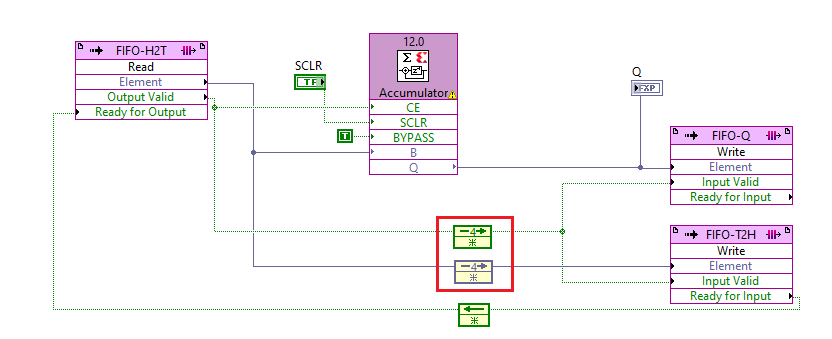

Finish ,然后将 IP 与 FPGA vi 中的其他组件连接起来。

注意 IP 的延迟

Latency 属性。

在接受到

有效输入后的

Latency个时钟周期延迟后,IP 将生成对应的

有效输出。

在本例中,延迟 Latency 为 4。因此,我需要在

有效控制信号上加上 4 个周期延迟。