To create a periodic trigger on the PXI(e) backplane using a R-series 78XX FPGA device, you can use its FPGA to generate the signal and route it to

【PXI_Trig】 node.

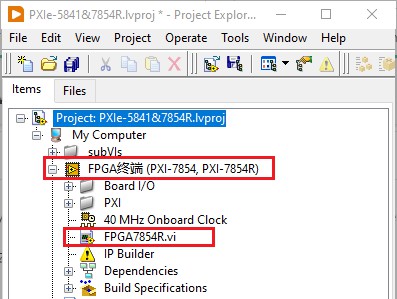

Let's use a PXI-7854 as a sample to show how to do this.

1. You need to create a FPGA target under your computer root in LabVIEW, and New a FPGA vi for it.

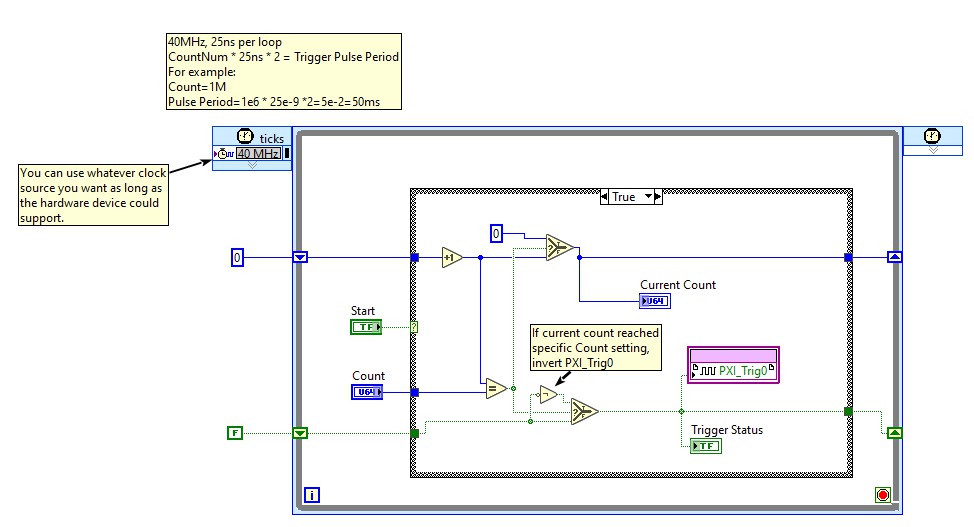

2. Open this FPGA vi, and build a simple state machine in the block diagram page.

3.

Compile FPGA VI into bitfile in order to call it in HOST VI.

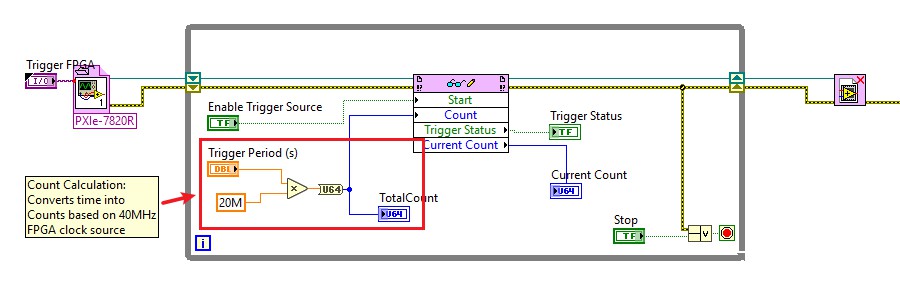

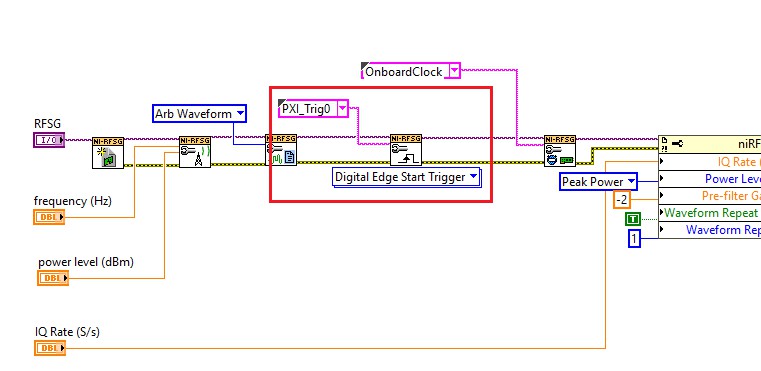

4. In HOST VI where you need to use this periodic trigger, you need to call it by 【

Open FPGA Reference Node】and 【

Read/write Node】

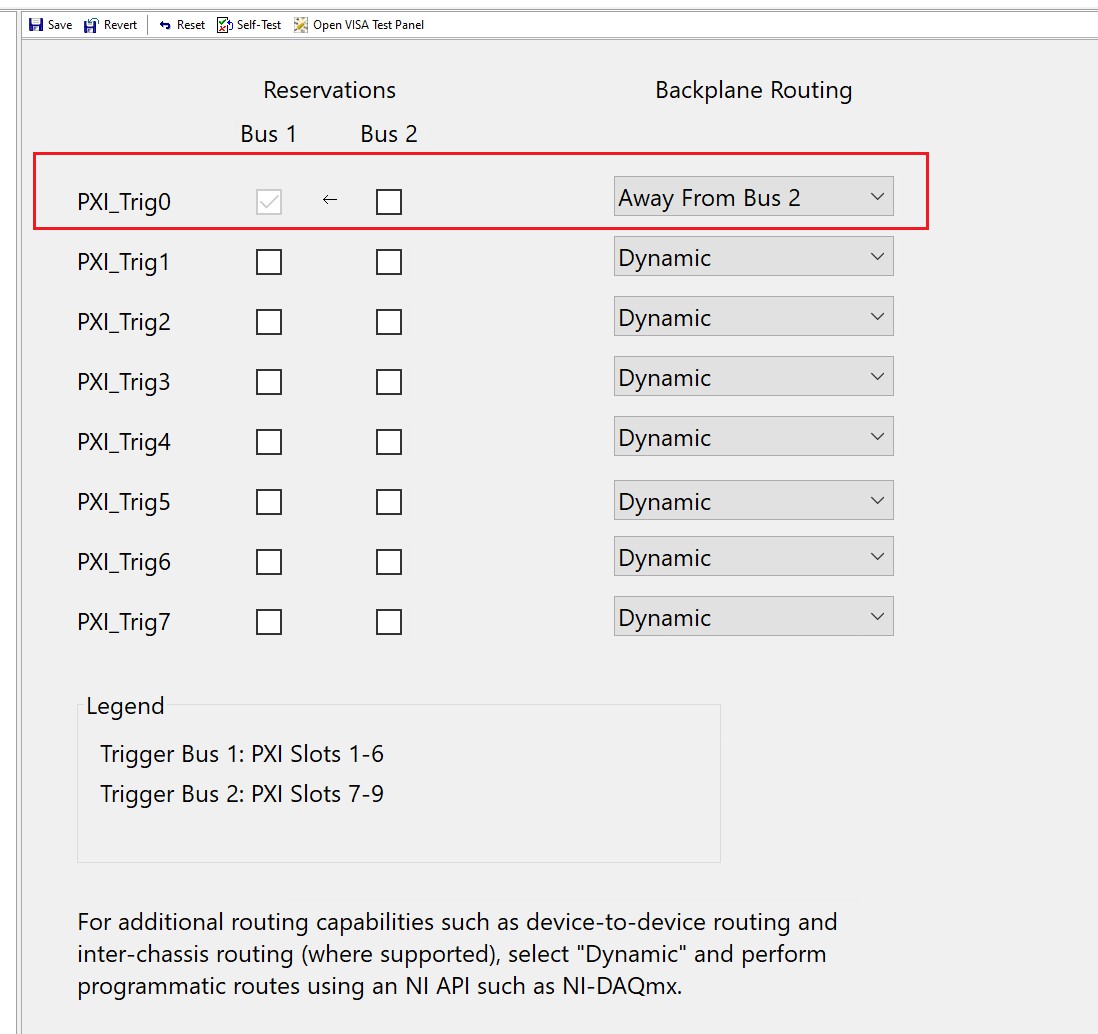

5. When you are using a

large PXIe Chassis, such as PXIe-1092 or PXIe-1095.There are

bus blocks on chassis backplane(as shown below).

If your R-series device(trigger source) and DAQ/VST(which is to be triggered) are installed in the slots which are on the different backplane trigger buses, please remember to

reserve the trigger bus for your use in advance.

Say if your PXI-78XX is in Slot 7 and your VST is in Slot 3, you need to configure backplane routing of PXI_Trig0 【

Away From Bus 2】in NI-MAX Chassis Page, Triggers Tab.

6. Finally step, you need to configure the trigger source of your DAQ/VST as 【

PXI_Trig0】in the code part.

NOTE:

NOTE:1. There is

up limitations for Periodic Trigger signal frequency on PXI Trigger Bus. Any signal with too high frequency probably will be invalid due to hardware issues. (Refer to related links)

2. Default state of PXI Trigger Lines is

Logic Level High.