本記事では以下の内容に分け案内を進められます:

1. 事前準備

2. サンプルプロジェクト概要と使用手順

3. シナリオに沿ったサンプルプロジェクト編集

*上記3のステップで紹介される編集されたVIは本ページからダウンロード出来るZIPファイルにまとめられております。

1. ソフトウェアインストールとサンプルプロジェクト作成

1.1. 下記ソフトウェアのインストール

・NI LabVIEW

・NI LabVIEW FPGAモジュール

・NI FlexRIO

1.2. サンプルVI の作成

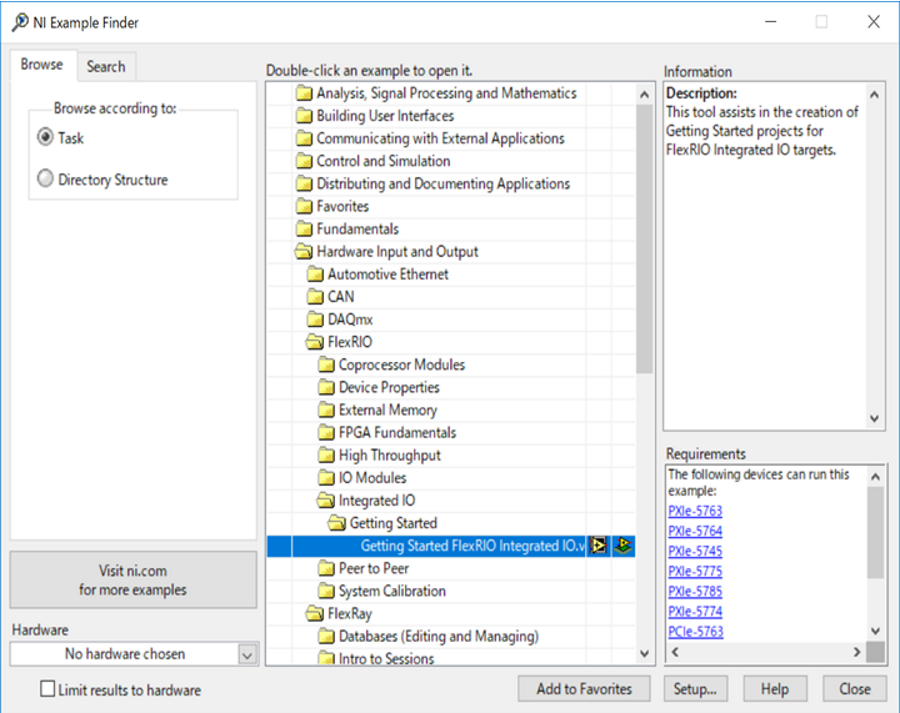

1.2.1. 今回使用するサンプルプロジェクトは「Getting Started FlexRIO Integrated IO.vi」

から生成します。

*サンプルファインダ起動後、ハードウェア入力と出力>>FlexRIO>>統合IOから呼び出し可能です。

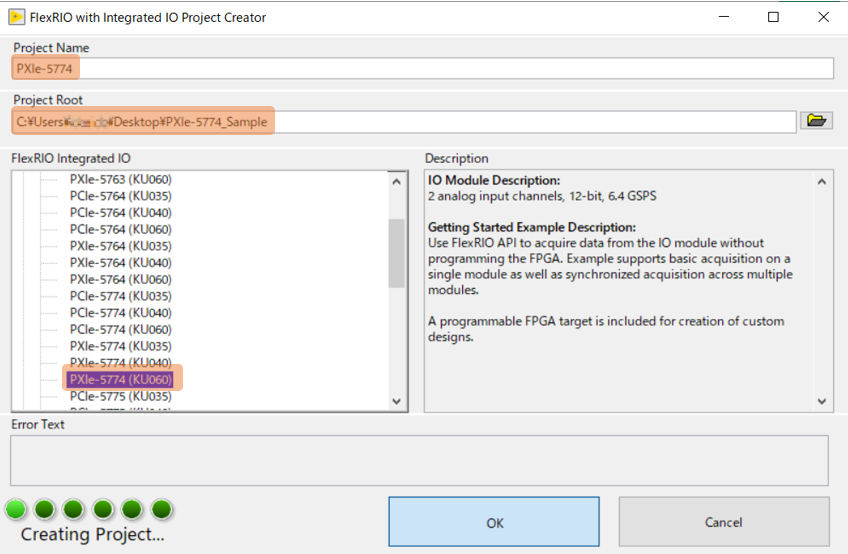

1.2.2 生成する際はプロジェクト名と保存先をあらかじめ入力し、使用するデバイスを選択し「OK」をクリックします。

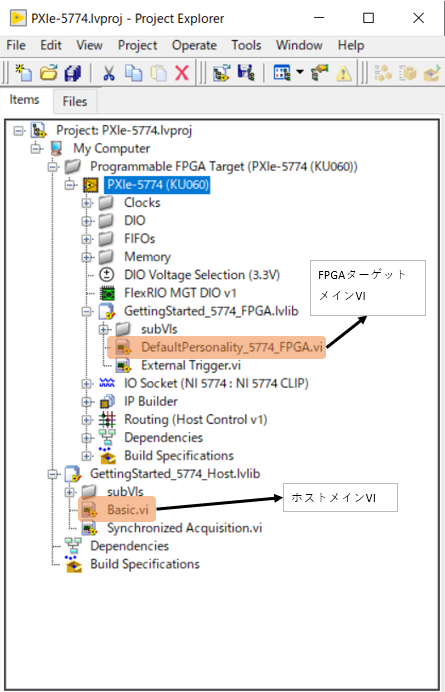

1.2.3. 実際に生成されたサンプルプロジェクトが以下の通り生成されていることを確認します。

*今回は画像内でハイライトされたVIを確認・編集します。

2. サンプルプロジェクト概要と使用手順

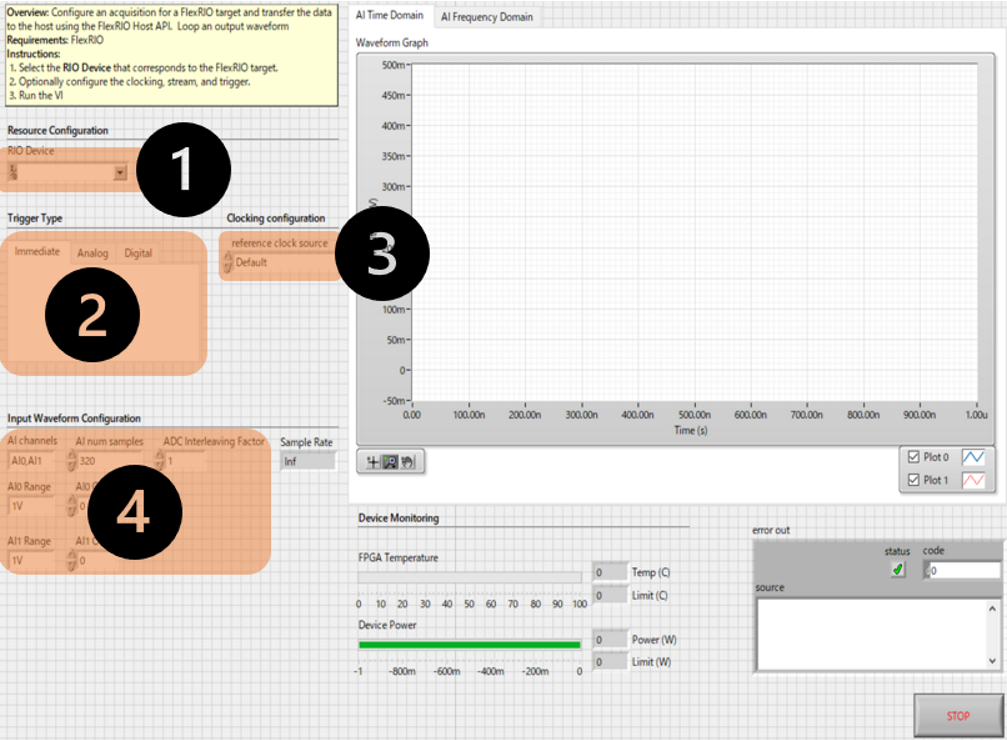

2.1. ホスト側MAIN VIのフロントパネル解説

①使用デバイス

②トリガ設定

③参照クロック

④計測チャンネル諸設定

2.2. 本サンプルプロジェクトを実行する際は”①使用デバイス”を入力し実行します。

*入力するデバイス名はMAXから確認し入力してください

2.3. VIが動作すると計測値が右上のグラフに表示されます。

3. サンプルプロジェクト編集案

ケースシナリオ:

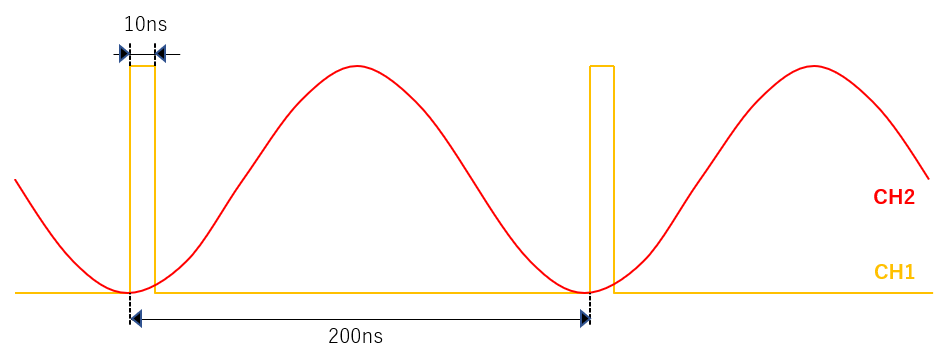

計測する二つの信号が以下の通り存在するとします。

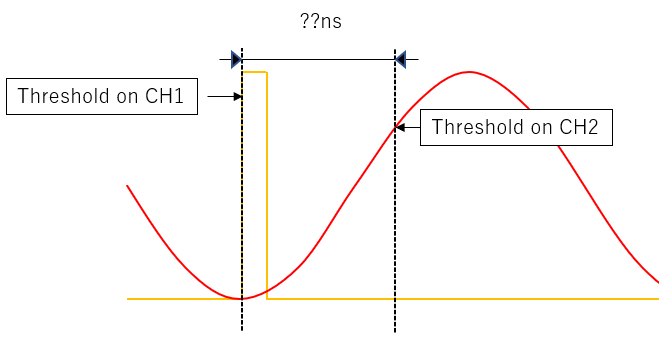

ターゲット上で、片方の信号が閾値越えしてから残りの信号が閾値越えするまでの時間を算出する処理を実装するものとします。

ホストVIでの実装手順は下記の通りとなります:

i. 各信号用にそれぞれの閾値を設定

ii. 入力信号の計測データを取得

iii. 2つの閾値間に存在する計測サンプルの数をカウント

iv. サンプル数を時間情報に変換し表示器に出力

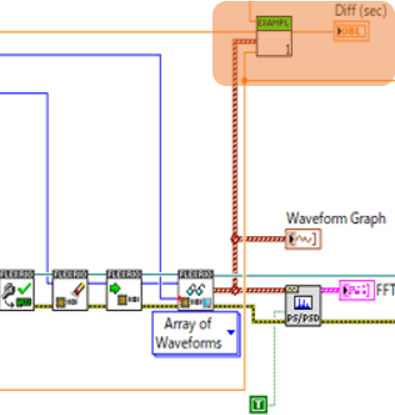

3.1. 下図、ホスト側読み取り関数後に後処理を追加します

3.2. FPGAターゲット側のメイン VIに追加処理を実装します

FPGAターゲットVIでの実装手順:

i. ホストメインVIから閾値情報を取得

ii. 片方の信号が閾値越えをしてからカウント開始

iii. もう片方の信号が閾値越えをしたらカウント停止

iv. カウントした数をホストメインVIから読み取り

v. それぞれの閾値を含めた二つの計測信号データをホストメインVIに送信

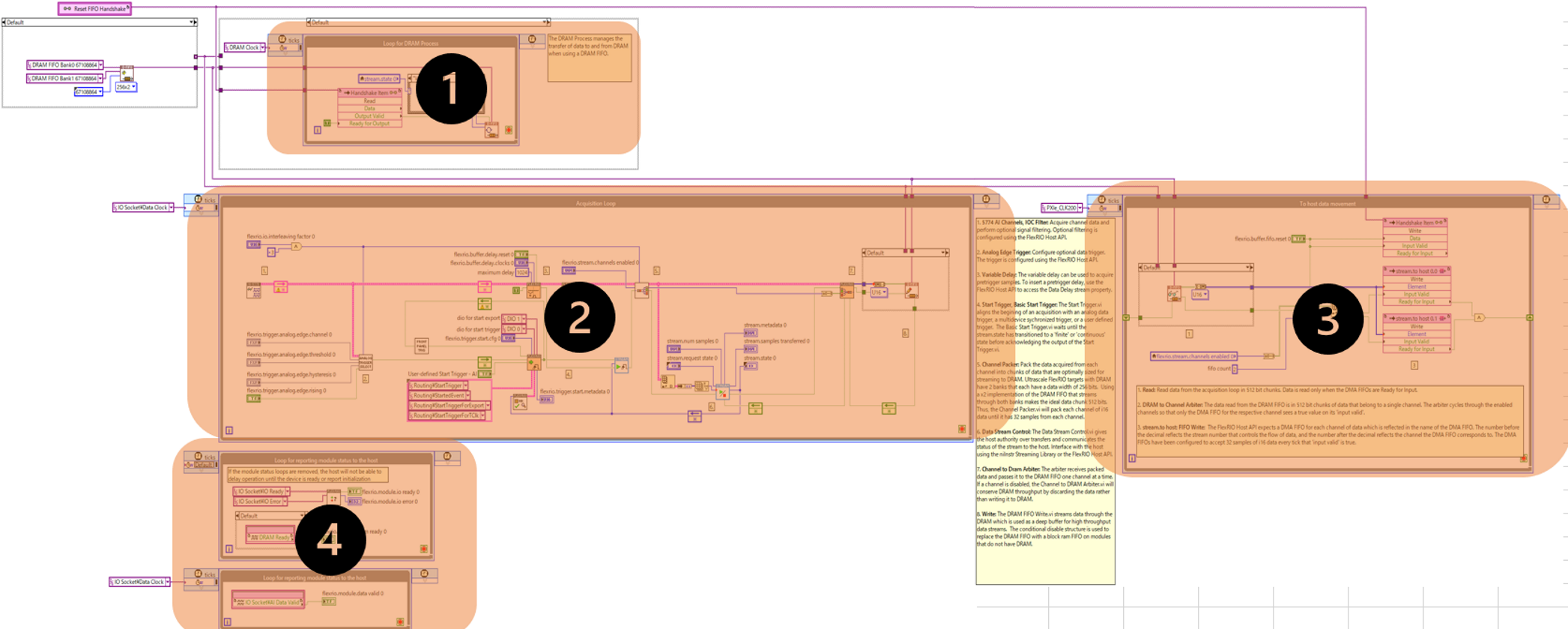

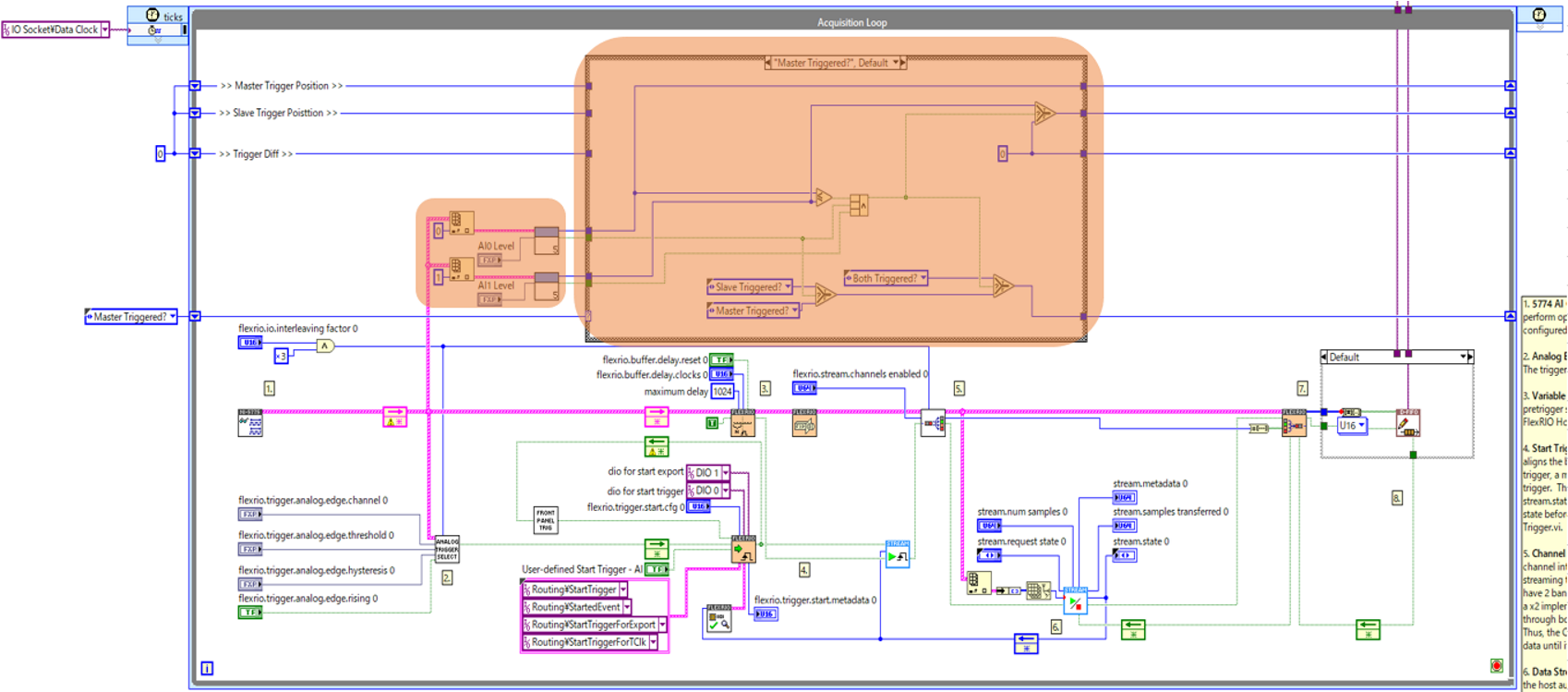

*下図FPGAターゲット用メインVI の各ループは以下の目的で実装されております。

① DRAM FIFOのステータス確認

②データを取得しトリガ待機、その後DRAM FIFOに格納するループ

③DRAM FIFOに格納されたデータをホスト側に転送するループ

④デバイス側のステータスを確認するループ

3.3. ループ②で計測が行われるのでタイミング違反に注意しながら追加処理を実装します。

下図ハイライト部分が目的の処理を行う為のブロックダイアグラム追加処理実装案をとなります。

3.4. FPGAターゲット用VIを編集後保存し、エラーなくコンパイル完了すること確認しホスト側メインVIを実行する。

追加情報

本記事ではホストメインVIとFPGAターゲットメインVIの両方に追加機能を実装する手順を案内しましたが、

追加機能の開発・実装の順序はホスト側から先に行うことが好ましい物となります。

処理速度の改善やホスト側リソースの節約を考える場合、FPGAターゲット側での実装が課題に上がりますが、

実装までに処理内容や使用関数の変更が求められるケースが多くかつコンパイルも修正の都度求められるので注意が必要となります。

FPGAターゲット側での実装を進める場合は以下3点の方法を用いて効率よく開発を進めることが求められます:

・追加実装処理をサブVIとして保存し、ホスト上で動作検証

・FPGAターゲットを”シミュレーション”モードで動かしロジックの検証

・コンパイルウィンドウを確認しエラーが発生した箇所を適宜修正