可以透過調整 IQ 增益來改善

LO 洩漏。若希望能完全擺脫它,我們可以利用發射機或接收機的數位頻寬將 LO 移出頻段外。但是這會導致裝置的可用頻寬減少。

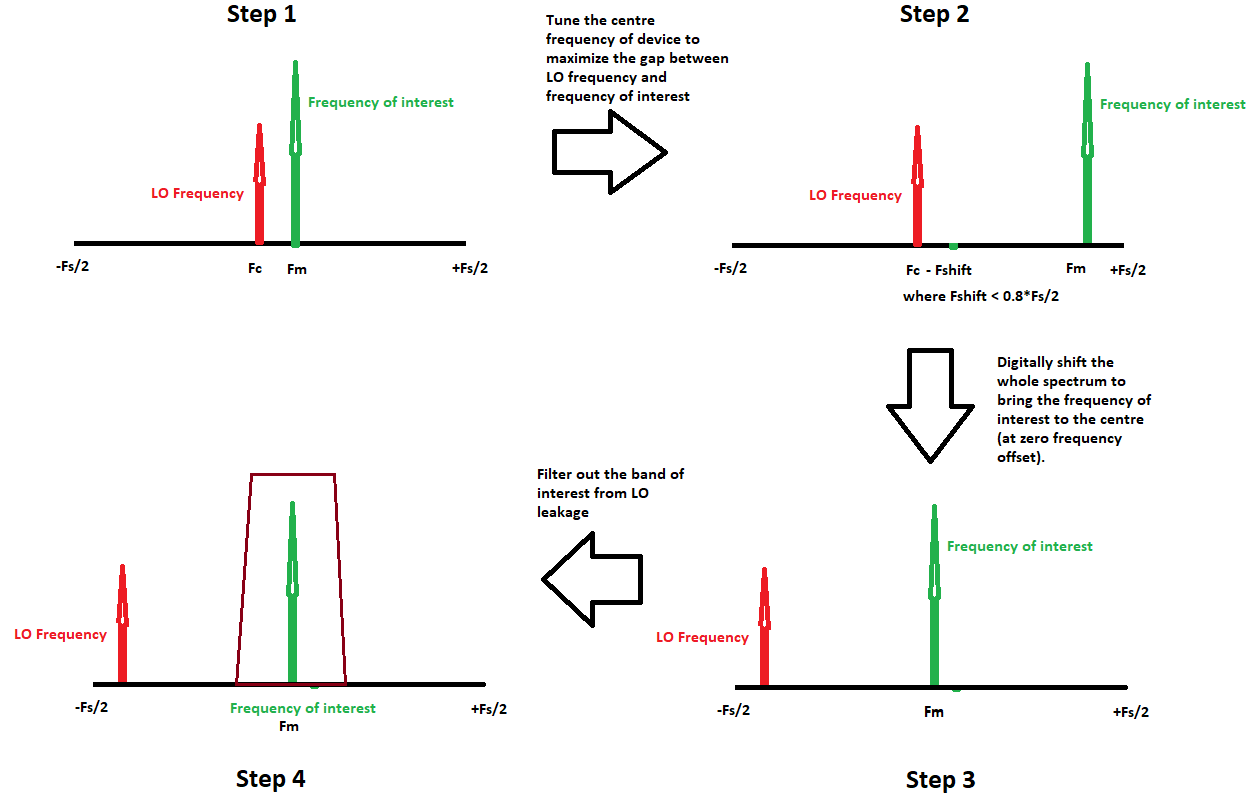

以下是將 LO 洩漏推到帶外所需執行的步驟。

- 觀察頻譜中感興趣的訊號頻率和頻寬。

- 調整您的裝置中心頻率,使 LO 洩漏頻率和感興趣的頻率之間的差異增加。例如,如果您想獲得 1.250GHz 的訊號,請將您的中心頻率調整為 1.220GHz,即距離實際訊號 30MHz(如果您的裝置的實時頻寬允許)。這將為您提供足夠的濾波器 roll-offs(滾降)空間,並定義您可以擁有的 LO 無洩漏頻帶。請注意,感興趣的頻率和 LO 洩漏之間的最大間隔限制為裝置頻寬的一半(通常為 0.8 * Fs/2,其中 Fs 是取樣頻率)。

- 我們通常需要零頻偏的message signal (消息訊號)或感興趣的頻率。然而在目前的情況下,我們真正要接收的訊號離中心很遠。為了把它帶到中心,我們需要應用一個數位頻移來轉換整個數位頻譜。

- 最後一步是消除 LO 洩漏。這通常透過抽取自動過濾掉它來完成。

下圖顯示了這四個步驟:

(Fs:取樣頻率,Fc:中心頻率,Fm:消息訊號頻率或感興趣的頻率,Fshift:通常將頻譜移動以在 Fc 和 Fm 之間建立空間的頻率)

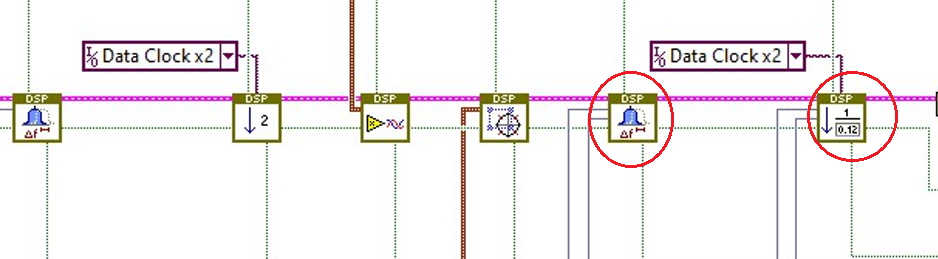

NI USRP RIO 簡單流專案已經在其 FPGA 程式碼鏈中包含了數位頻移和抽取 IP,如下所示。它們的值可以從主機設定。請參閱這些IP的 Help 文件以了解設定選項。

類似的概念可以應用於其他 NI RF 裝置,例如 NI 向量訊號收發器。

可以使用Downconverter Frequency Offset (Hz) Property 進行數位偏移。