NI VeriStand Engine Architectureの理解

NI VeriStandでシステムを開発するにあたり、VeriStand Engine Architectureを理解することは非常に重要です。VeriStand Engineはシステム全体のタイミングや、ホストとターゲット間の通信を制御します。複数のループから構成されており、個々のループには優先度とデフォルトの実行レートが定義されています。下図の

H/M/Lは、それぞれ

高/中/低優先度を示しています。

VeriStand Engine - VeriStand Help

NI VeriStandのベンチマーク

最適化を行うにあたり、現在のパフォーマンスを測定することが必要です。NI VeriStandのSystem Channelsにある以下のチャンネルを観測し、パフォーマンスを測定します。

- Actual Loop Rate: 設定したPrimary Control Loop (PCL) に対する、実際の実行レート

- HP Count: 高優先度ループの処理が間に合わなかった回数。ゼロであることが望ましい

- LP Count: 低優先度ループの処理が間に合わなかった回数。ゼロであることが望ましい

- Model Count: モデル実行が間に合わなかった回数。ゼロであることが望ましい

シミュレーションモデルを使用している場合は、以下のチャンネルも観測します。

- Time Step Duration: モデル実行に要した時間

どのような場合でも、Actual Loop Rateを確認することが重要です。Actual Loop Rateによって、システム全体の処理速度やジッタの大きさを確認することができます。

パフォーマンスの最適化

パフォーマンスの最大化

- Streamlining the System Definition

- 使用しないデバイスは、プロジェクトから削除または無効化します。

- DAQのConversion Clock RateをMaximumに設定します。

- ソフトウェアタイミングでなく、ハードウェアタイミングを使用します。詳細は本資料の「Primary Control Loopのタイミングソース」セクションをご覧ください。

- Configure the BIOS settings of the controller

- Turbo Boostを有効にします。この操作により、ジッターが増える可能性があります。

- Enabled CPU Coresを減らします。デフォルトはALLに設定されてます。

- Asynchronousカスタムデバイスなど非同期要素において、別のCPUコアを明示的に割り当てます。

- Configure the Ethernet settings of the controller

- Select hardware for performance

- ハードウェアタイミングをサポートするコントローラを使用します。

- 同時サンプリングをサポートするDAQデバイスを使用します。

- CANバスモニタを行う場合、USB CANデバイスの仕様を検討します。

- PXIeデバイスまたはコントローラを使用します。

- NI Real-Time Hypervisorを無効にします。

- Improve model performance

- 複数の小規模モデルを大規模モデルに統合し、メモリ使用量を減らします。

- LabVIEWで作成したモデルの場合、配列連結などの関数は使用せず、配列初期化関数などで事前に配列を割り当てます。

- Optimize reflective memory

- Reflective Memoryを使用している場合のみ、参照します。

コントローラの実行モード

VeriStand Engineの実行モードには2種類あります。要件に応じて一方を選択します。

各モードにおけるVeriStand Engineの実行順序については

Primary Control Loop Execution Steps を参照します。

- Parallel (Default): PCLはモデルの実行を開始すると、モデルの実行完了を待たず次の処理に遷移します。このためモデルが生成したデータをシステムで利用するまでに、1サイクルの遅延が生じます。

- Low Latency: PCLはモデルを実行し、実行完了を待機します。モデルが生成したデータを、そのサイクル内で使用できます。Paralellで見られた1サイクルの遅延はありませんが、モデルの実行時間がPCL Rateに影響します。

手動でのCPU割り当て

必要に応じて、各ループに手動でCPUを割り当てることができます。

モデルの場合、Execution Orderページでモデルの複数モデルの実行順序を逐次または並列に設定できます。

モデル単体の実行時間が間に合わない場合、モデルを互いに依存関係のない状態に分割化し、それぞれを並列実行することが考えられます。

Decimationの利用

Decimationは、PCLレートに対して低優先度タスクの実行レートを落として、システム全体の負荷を軽減するために使用します。

例えばModel Processing Loopの場合は、

Model Rate = PCL Rate / Decimation

となります。PCL Rate = 100Hz、Decimation = 2の場合、Model Rateは50Hzとなります。Model Processing Loopの他に、Data Processing Loopに対してもDecimationを設定できます。

Primary Control Loopのタイミングソース

PCLのタイミングソースは、PCLループのタイミングソースです。以下のオプションから選択します。

- Automatic Timing: VeriStandは自動でタイミングソースを決定します。シャーシの構成ページで Chassis master hardware synchronization device が指定されている場合、そのデバイスをタイミングソースとして使用します。この項目が指定されない場合、VeriStandは最初に利用可能なタイミングデバイスを選択します。

- DAQ Timing: VeriStandはシステム内のDAQデバイスをタイミングソースとして使用します。このオプションを有効にするには、少なくとも1つのアナログ入力チャンネルを持つDAQデバイスを構成ツリーに追加します。

- Custom Device Timing: VeriStandは、指定されたカスタムデバイスをタイミングソースとして使用します。

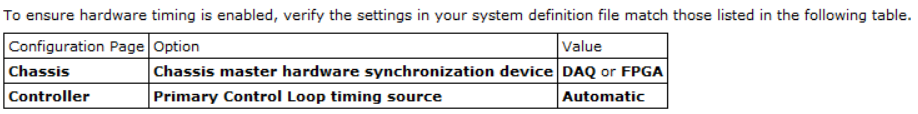

パフォーマンスを最大化するために、ハードウェアタイミングを使用することが推奨されます。

Chassis master hardware synchronization device の設定がDAQまたはFPGAであり、PCLのタイミングソースがAutomaticであることを確認します。

VeriStand Help Guidelines for Maximizing System Performance より

formance

XNETループの設定

VeriStandはデフォルトで、CANのIncoming / Outgoing フレームを非同期カスタムデバイス内で実行します。これはXNETループとPCLとの間で、読書きに1サイクルの遅延が生じることを意味します。送受信フレームの処理レートは、Incoming frames processing rate[Hz] または Outgoing frames processing rate[Hz] で設定します。

この遅延をなくすためには、Inline Incoming Frames または Inline Outgoing Frames を有効にします。このオプションを選択すると、XNETループはInline HW Interfaceカスタムデバイスと同等の動作をします。

その他、パフォーマンスに関連するKnowledge等については関連リンクの項目をご覧ください。