1. Drop I/O Nodes

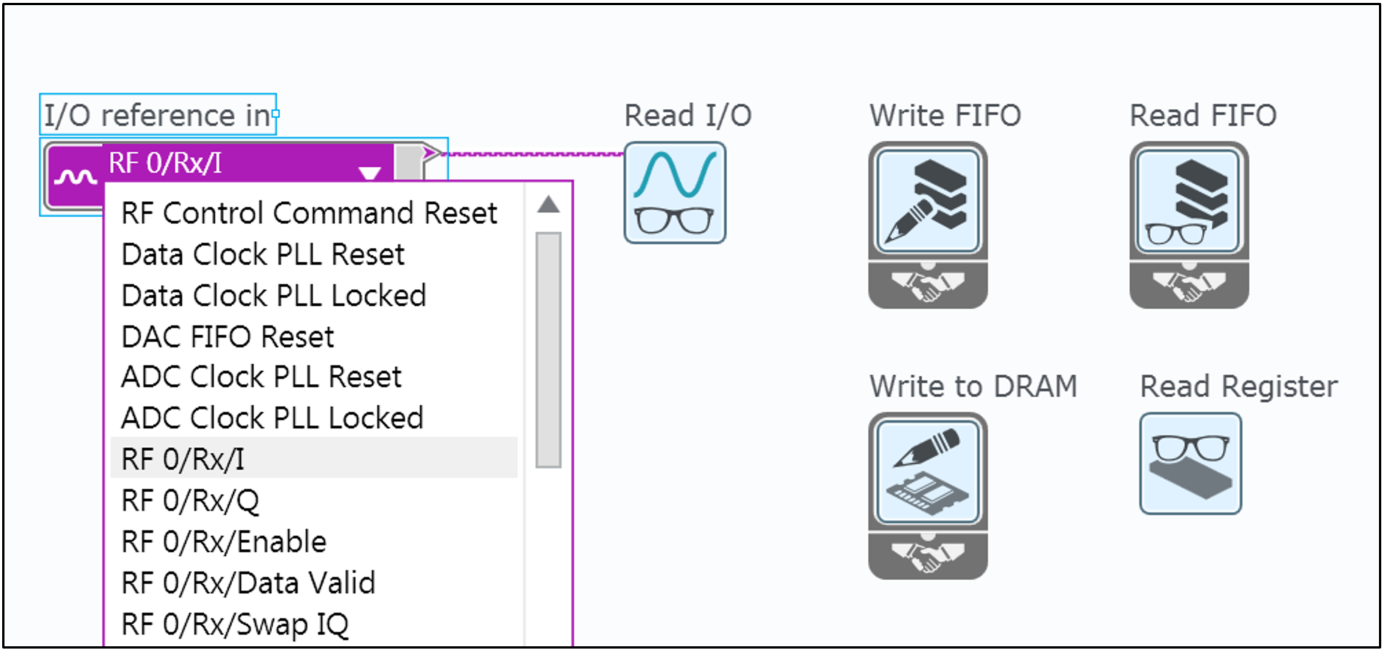

To interface FPGA algorithms with the ADCs and DACs that connect to the RF front ends, a host CPU, or resources such as memory, simply drop a Read or Write node for that resource. See Figure 2 for some examples of these nodes.

Figure 2. Use blocks like these to communicate with real-world I/O, FIFOs moving data to and from the host CPU, the DRAM on the USRP RIO device, or registers.

2. Configure I/O Nodes

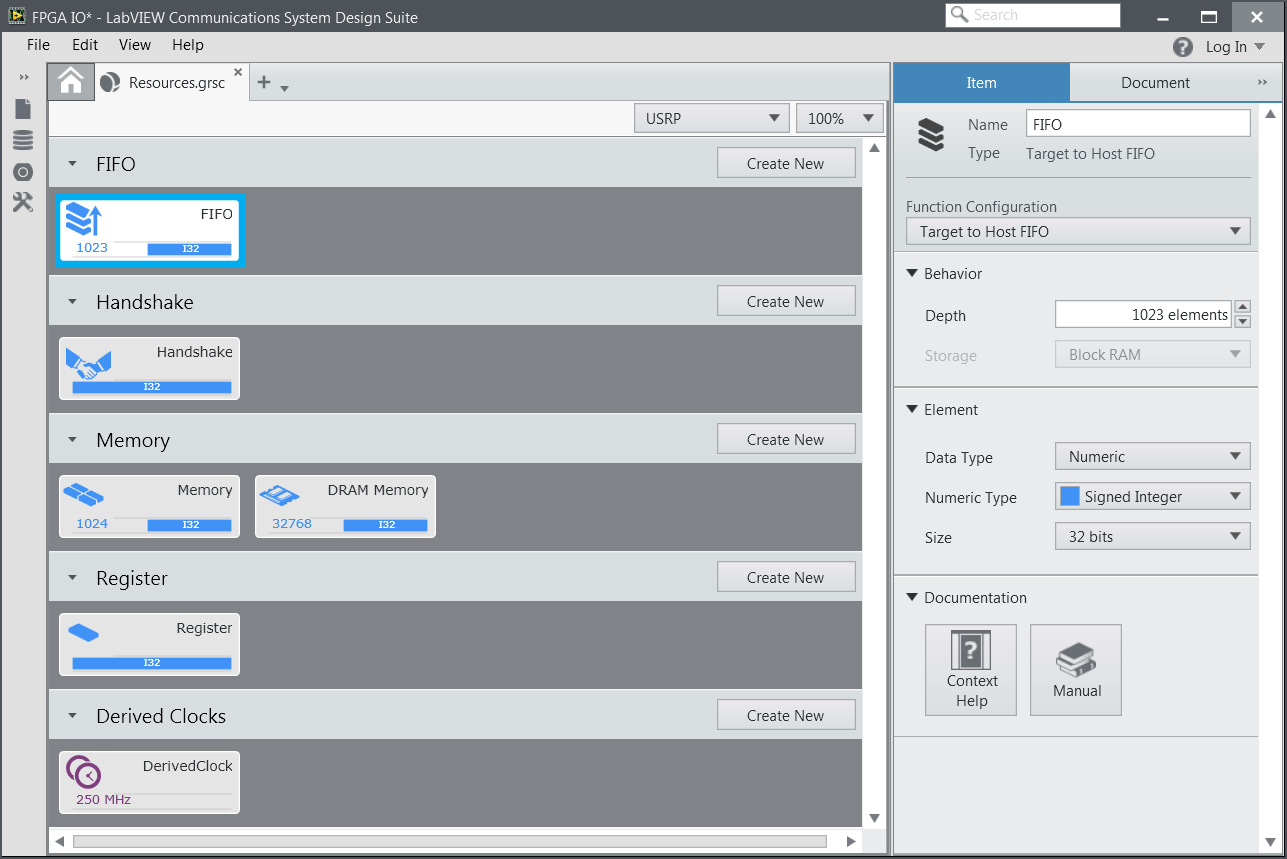

You can configure FPGA I/O resources using a resource file, as shown in Figure 3. Configure properties like resource alias, data type, direction (FPGA to host, host to FPGA, FPGA to FPGA, local), or buffer depth.

Figure 3. Use a resource file to create and configure FIFOs, memory, clocks, and other resources.

Figure 3. Use a resource file to create and configure FIFOs, memory, clocks, and other resources.

3. Connect Algorithms to I/O Nodes

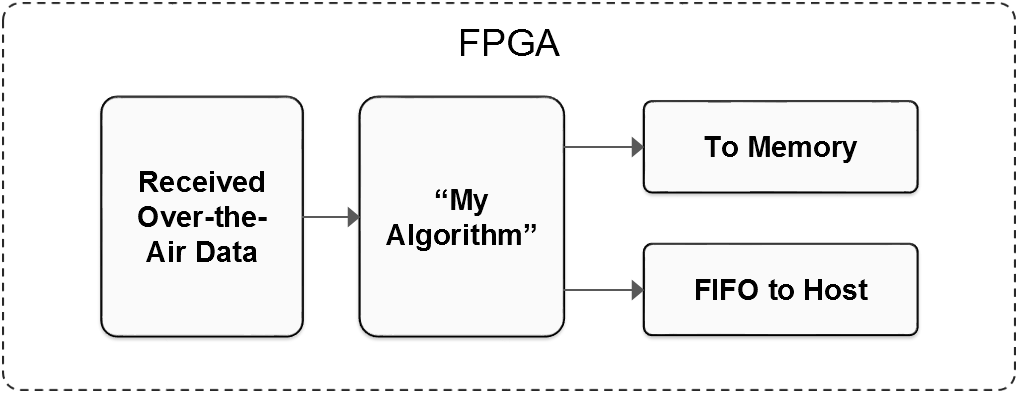

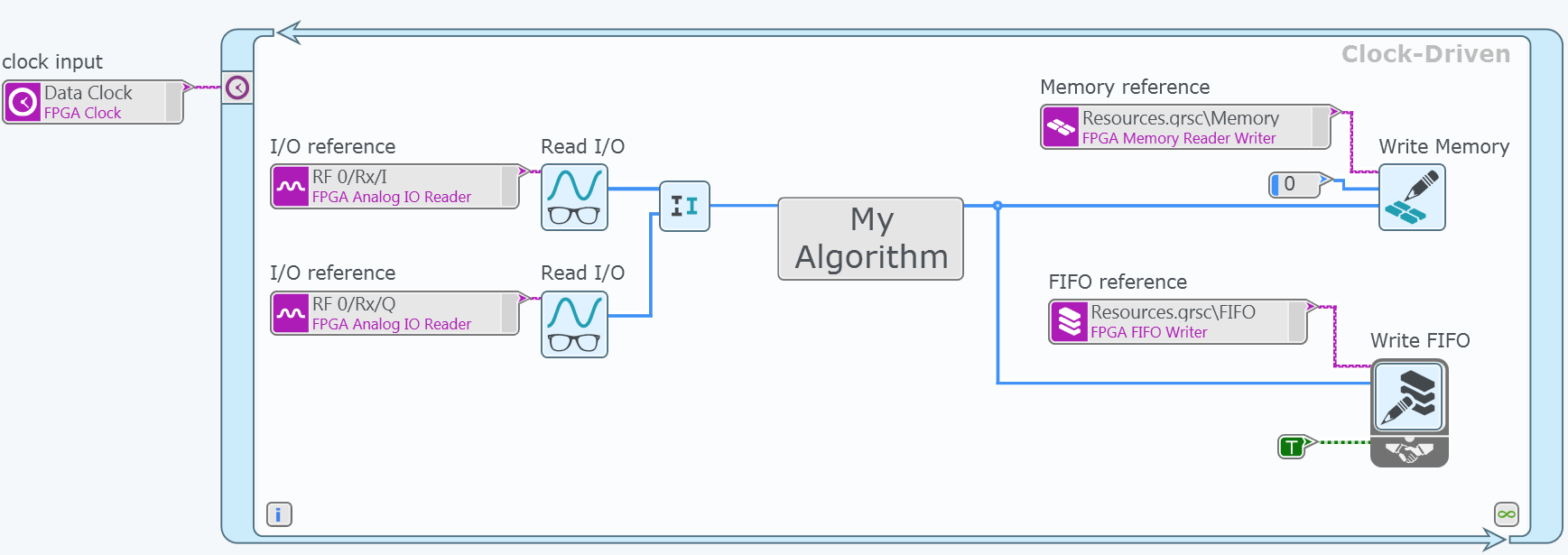

Once you have created and configured your desired resources, you can connect them to the algorithms you implement on the FPGA. For example, the block diagram in Figure 4 was implemented on the FPGA in LabVIEW Communications (see Figure 5). In the design, data from the receive port of the USRP RIO device is streamed into “My Algorithm” on the FPGA, which could be any block like synchronization, demodulation, or a filter. The output is then streamed to memory and an FPGA-to-CPU FIFO.

Figure 4. This block diagram of the example design shows how data is received from the RF front end, processed by a user-created block called “My Algorithm,” and streamed to memory and the host CPU. My Algorithm could be any algorithm such as demodulation, filters, or fast Fourier transforms.

Figure 5. In this implementation of the theoretical block diagram in FPGA code in LabVIEW Communications, raw I and Q data is read from the RF front end, processed by My Algorithm, and then streamed to memory and to the host CPU.

4. Consider What’s Next

To write a custom, real-time block like My Algorithm on the FPGA, you do not need VHDL experience when you use LabVIEW Communications. To learn how to create an algorithm like a 20 MHz orthogonal frequency division multiplexing (OFDM) modulator, continue to the next instalment of this Tips and Tricks series, “Go from a Concept to FPGA Code with No HDL Expertise.”