Issue Details

I know that the 4 RF channels on a USRP X410 could work independently for sure.

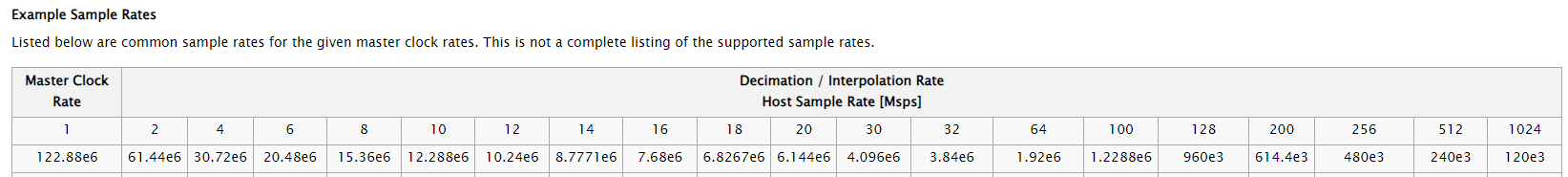

Now I'm wondering how to actually code it to achieve having different sampling rate on each RF channel of an X410 like the table we listed

for N310:

How do we actually implement this (in terms of UHD code) on a X410?