Issue Details

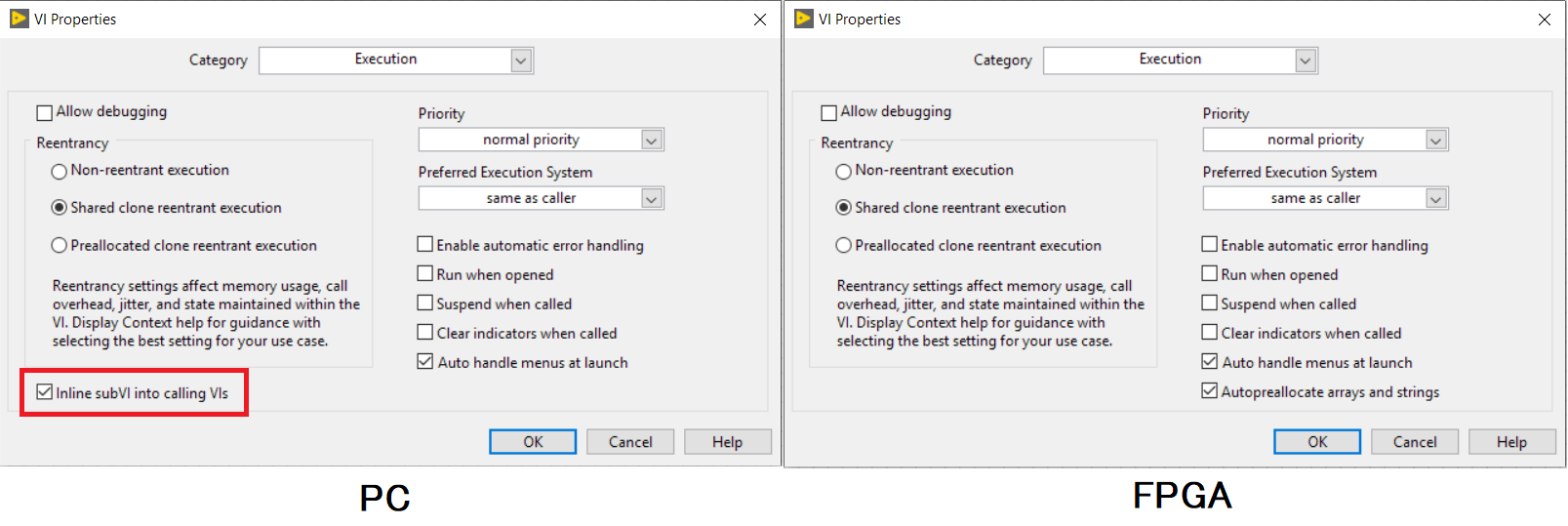

I have created some VI for my PC and I might like to compile the code for cRIO FPGA targets in some cases. I found that if you want to compile a VI for an FPGA the option to inline the VI is not available.

- Why is this option not allowed?

- How does it affect the performance of the VI?

- Do I have to create a copy of the VI so I can avoid errors during compilations if the VI for the FPGA is originated from a host VI with Inlining enabled?