Solution

This issue is generally caused by a packet mismatch between the number of packets listed as being read/written in your custom .fpgaconfig XML file, and the number of packets your FPGA code is actually reading/writing.

The number of packets written by your code will depend on your specific project -

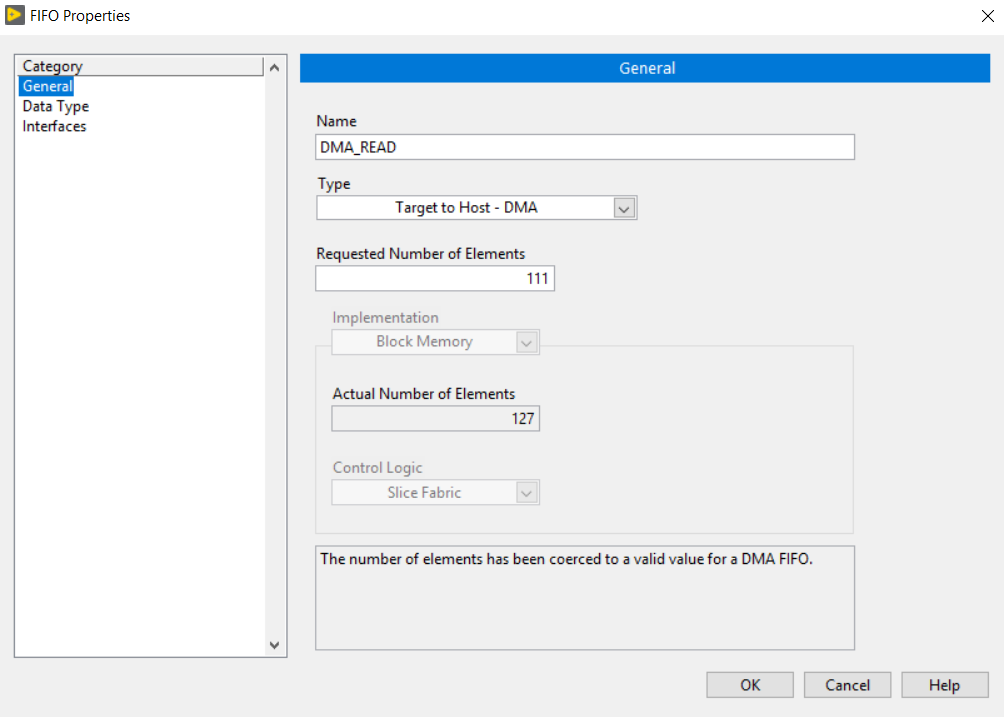

Note that the size of your DMA FIFO is not equal to the number of packets being sent by your code. Generally, you'll want to ensure the DMA FIFOs for your reading and writing are at least twice as large as the largest amount of packets you expect to accommodate bidirectional communication.

The DMA FIFO Properties page will coerce your requested value to the nearest possible value for your system.

If you created your custom .fpgaconfig XML using the

information provided by NI in VeriStand's help documentation, you'll be able to open it in a web browser or XML editing software like XML Notepad and ensure that your specified packets correctly match your expected reads and writes from your code.