To execute a Single Cycle Timed Loop (SCTL) at a rate other than the default 40Mhz, you first need to create a new FPGA derived clock at your desired rate. FPGA derived clock rates can be specified between 5 MHz and 800 MHz.

To create a derived clock,

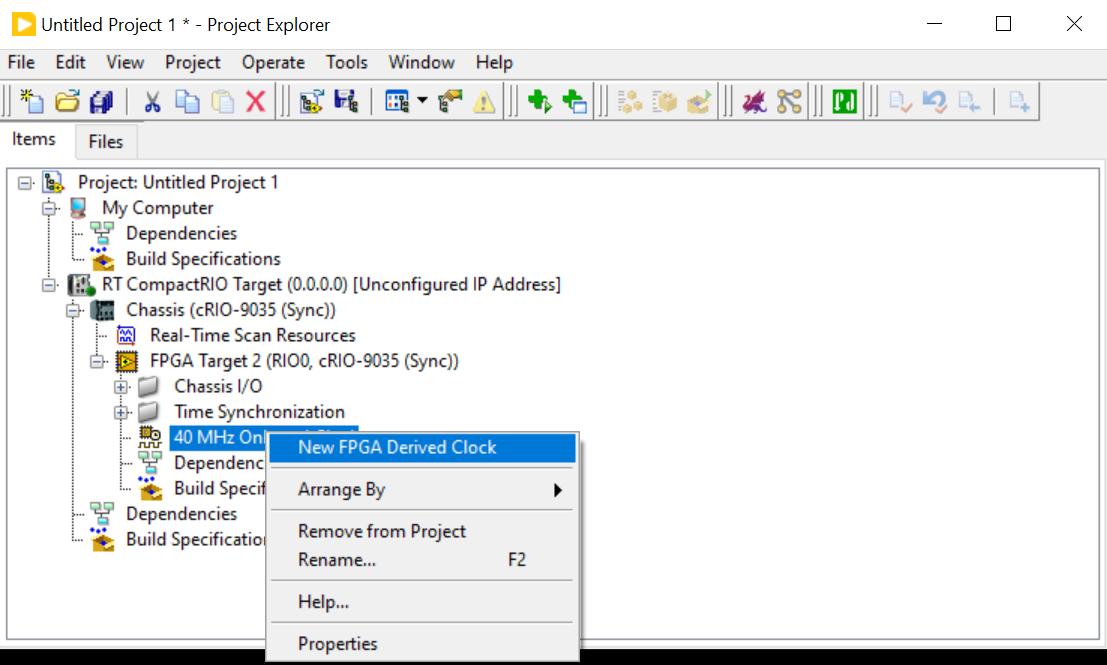

- Right-click the 40MHz Onboard Clock in your project explorer window

- Select New FPGA Derived Clock

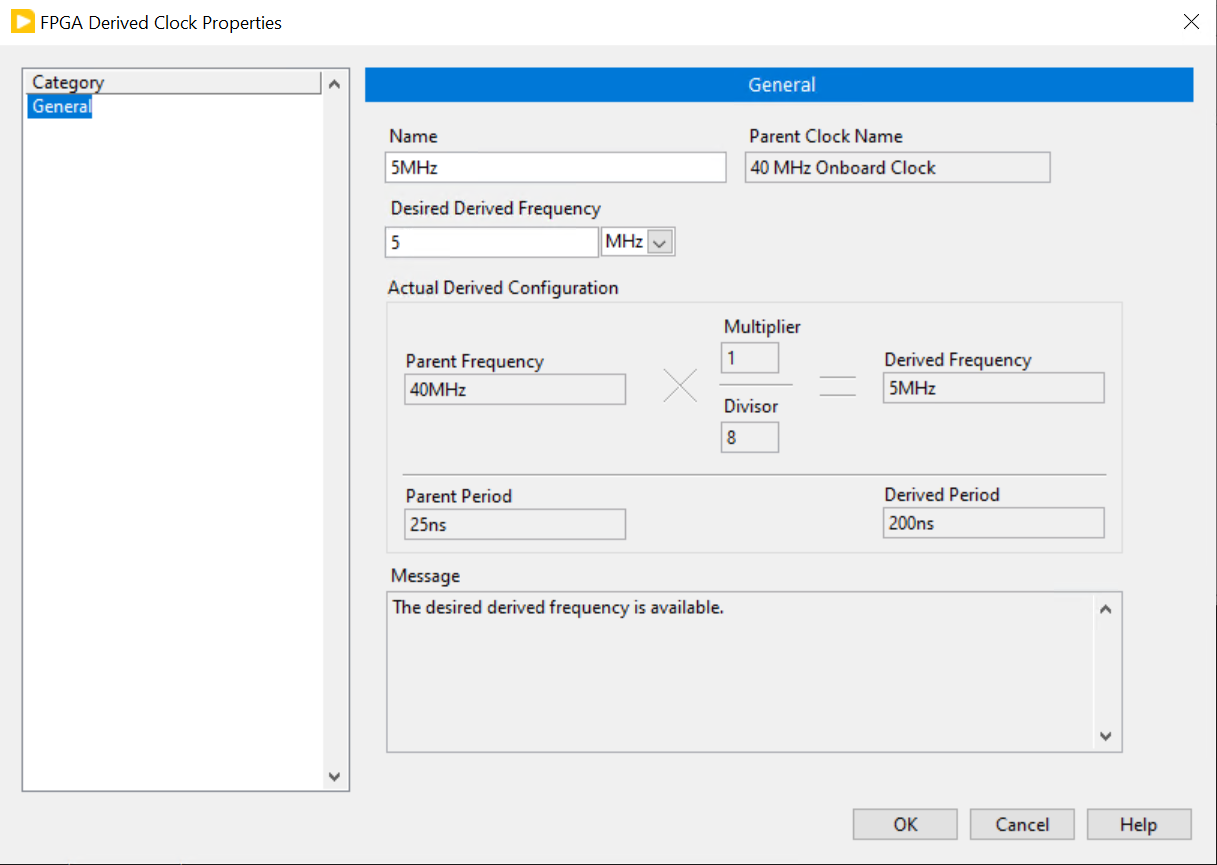

- In the FPGA Derived Clock Properties window, you can adjust the clock Multiplier and Divisor to achieve your desired clock rate. Pay close attention to any comments generated in the Message field, they will let you know if you have requested a valid configuration.

To configure the SCTL to use the new derived clock,

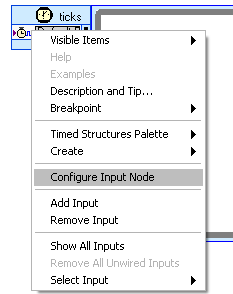

- Right click the left hand timing block of the SCTL and select Configure Input Node.

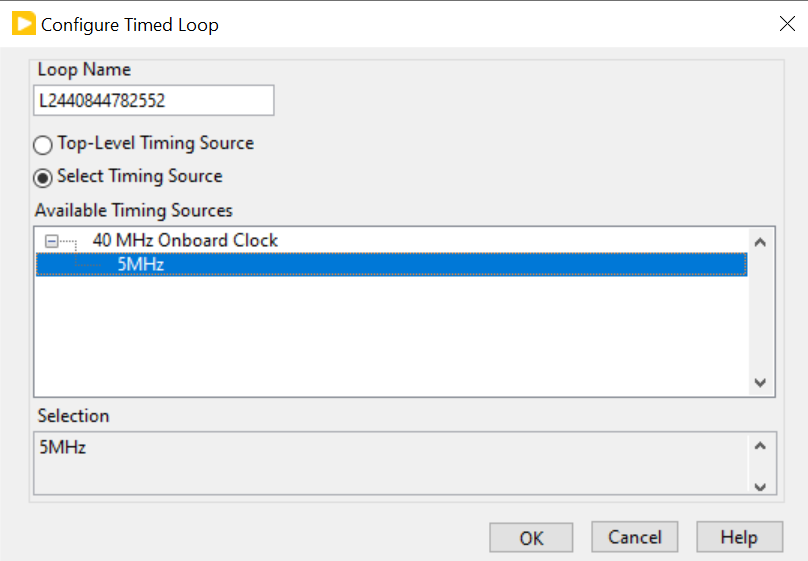

- In the Configure Timed Loop dialog, select the Select Timing Source radio button and click your derived clock under Available Timing Sources and click OK.

Note: Some code may not compile at rates above 40MHz, due to timing constraints of the FPGA. The compilation report summary will list an error if your code was not able to be compiled at the derived clock rate.

Additional Information

If none of these rates are suitable for your application, you should review this example program Configure Sample Rate of Single Cycle Timed Loop in LabVIEW which demonstrates how to configure a sample rate outside the allowed range of a derived clock.