Physical Setup:

The PXIe-5831 module is a 4-slot module, so you can fit up to 4 devices in a single PXI chassis such as PXIe-1095, which is equivalent to 4x4 MIMO system. This can be expanded to Multi-Chassis synchronous system by sharing the Reference Clock and triggers from one chassis to another using Timing and Synchronization Module.

For a single chassis setup, follow the below steps to setup your phase coherent configuration:

- Insert your PXIe-5831 modules adjacently (side to side) in the chassis

- For the PXIe-5831 module setup, follow the steps described in the device getting started manual to configure the PXIe-5820 with the PXIe-3622

- Select your Leader device (typically the most right or the most left device)

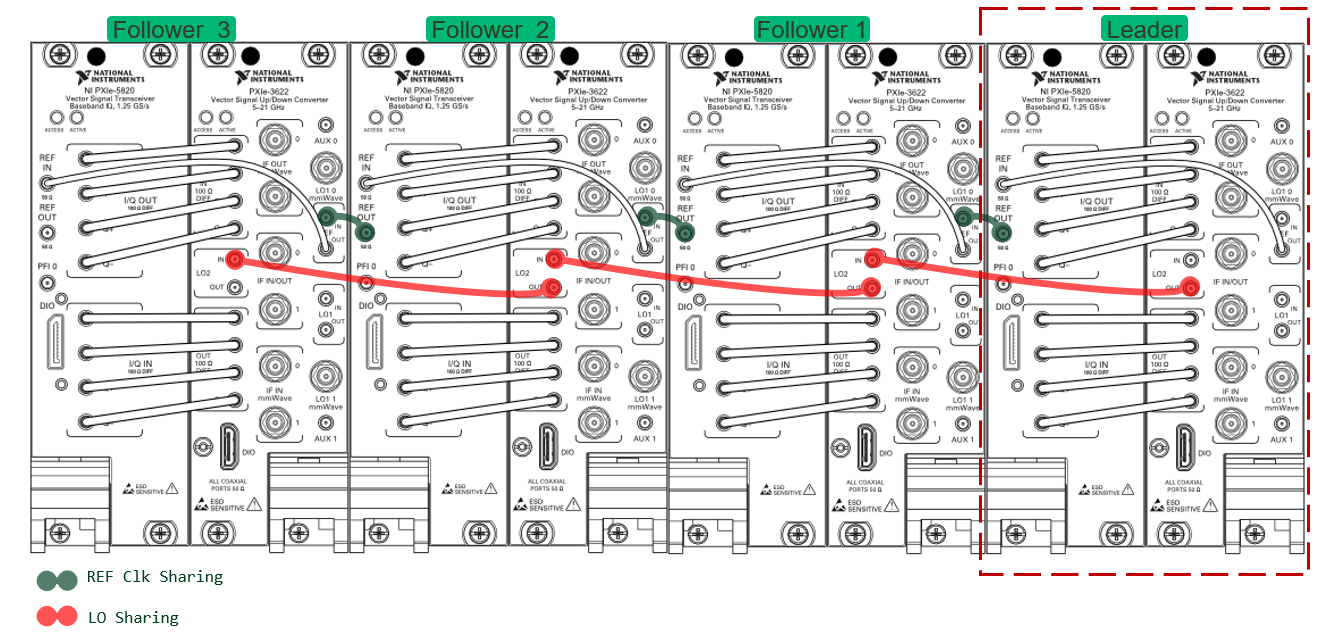

- Using mmpx cables of matching length, connect the LO2 OUT of the Leader device to the LO2 IN of the adjacent device (Follower 1), and LO2 OUT of Follower 1 to LO2 IN of its adjacent device (Follower 2). Follow the same to share LO between all devices in your chassis

- Using mmpx cables of matching length, connect REF OUT of Leader to REF In of Follower 1, then REF OUT of Follower 1 to REF IN of Follower 2, etc...This will share the onboard Ref clock of the Leader with all the Followers. IF you would like to use PXI Reference clock as a reference, you can skip this step and you can configure it using the driver APIs as we will see in the Software section.

- The connections should look like this:

Software Configuration:

In the previous section, we discussed how we can synchronize the Leader device with the Following devices by sharing the LO and Reference Clock. In this scenario, the Leader is programmed to distribute the trigger signal to all Followers in the system including itself. Two issues that arise here are trigger delay and skew. A trigger delay from the Leader to all the Followers and skew between each Follower device is inevitable, but this delay and skew can be measured and calibrated. To overcome this situation,

NI-TClk synchronisation is used where its purpose is to have devices respond to triggers at the same time. The "same time" means on the same sample period and having very tight alignment of the sample clocks.

NI-TClk synchronization is accomplished by having each device generate a trigger clock (TClk) that is derived from the sample clock. Triggers are synchronized to a TClk pulse. A device that receives a trigger from an external source or generates it internally will send the signal to all devices, including itself, on a falling edge of TClk. All devices react to the trigger on the following rising edge of TClk.

NI-TClk has a set of APIs that can be called from LabVIEW to enable the homogeneous trigger alignment.

That being said, to configure a phase coherent multi-channel system, we need to set several properties for NI-RFSA and NI-RFSG such as the LO sharing and Reference clock, as well as enable the NI-Tclk trigger alignment between the devices.

For the PXIe-5830/1, there are few properties that need to be set in addition to those in a 5840/1 based system. For instance, you need first to set the selected ports for transmission and reception since the IF ports of the 5830/1 are bidirectional.

In addition, for the PXIe-5831 VST, you need to manually set the active LO channel you are targeting to configure since there are 2 LOs, LO1 used for the mmWave head connections and LO2 used for the IF path. In our case we will configure the LO2 channels.

Here is a summary of the steps required to configure RFSA/RFSG for Phase Coherent acquisition and Generation:

Configure Port:

To configure selected port with RFSA and RFSG, you need to place a driver specific property node.

For RFSA, navigate to Signal Path >> Advanced >> Selected Ports, possible values for IF mode are if0 or if1

For RFSG, navigate to Device Specific >> Vector Signal Transceiver >> Signal Path >> Selected Ports, possible values for IF mode are if0 or if1

Configure Reference Clock:

To Set Reference clock, we mentioned several methods:

- Leader shares its onboard reference clock with the Follower device, and each follower with its adjacent device in daisy chain mode. This means you need to set the Leader Reference Clock to Onboard and the Follower reference clocks to RefIn while enabling the reference clock export to RefOut terminal.

For RFSG, use the niRFSG Configure Ref Clock .vi to set the reference clock, and enable the reference clock export for the Leader and all Followers except the last one (since it is not sharing its signals with any other device), using niRFSG property node by navigating to Clock >> Reference Clock Export Output Terminal

For RFSA, use the niRFSA Configure Ref Clock .vi to set the reference clock, and enable the reference clock export for the Leader and all Followers except the last one (since it is not sharing its signals with any other device), using niRFSA property node by navigating to Clocking >> Ref Clock Exported Terminal

- Leader and Followers are all synced to the PXI Reference Clock, assuming that the selected chassis provides an onboard OXCO clock source, for instance the PXIe-1095 has 2 options with and without onboard clock. Verify that your chassis provides access to a 10MHz reference clock before proceeding with this step.

For RFSG, use the niRFSG Configure Ref Clock VI with the PXI_CLK property as source for all devices:

For RFSA, use the niRFSA Configure Ref Clock VI with the PXI_CLK property as source for all devices:

- Leader and Follower can all be synched to an external Reference Clock, in this case use the previous step with RefIn as a value for the clock reference source

Configure LO Sharing:

For the daisy chain setup, the Leader exports its onboard LO2 to the adjacent Follower device and each Follower with the next adjacent one.

With RFSA, using a niRFSA property node, you need to set in order, first the

Active Channel with value=

lo2, followed by the LO Source (

Signal Path >> LO Source) and the LO Export Enabled property (

Signal Path >> LO Export Enabled) . The LO Export needs to be enabled for the Leader and all Follower devices sharing their LO (except the last one).

The LO Source on the Leader needs to be set to

Onboard, unless you are using an external LO synthesizer such as the PXIe-5653, where you can set the source to

LO_In.For the devices receiving external LO, you need to set the LO frequency using niRFSA property

SignalPath >> LO Fequency, where you read this value on the sharing device and you wire it to the receiving device.

Note - Setting LO Power:

It is important to note that the accepted power for LO In is between 6 and 10dBm, so your external LO should follow this range, including the power output by LO2 from the Leader. The default power output from LO2 is around 5dBm, so you need to manually set the value of LO Out Power between 6 and 10 dBm before inputting the LO In Power to the Followers .

For niRFSA, You can access the LO power property from

SignalPath >> LO Out Power

With RFSG, follow the same steps as with RFSA. Navigate to

RF >> LO Out Enabled to export LO,

RF>>LO Frequency (Hz) to read and write the LO frequency and

Device Specific >> Vector Signal Transceiver >> Signal Path >> LO Source to set the LO Source.

To Set the LO Power property navigate to

Device Specific >> Vector Signal Transceiver >> Signal Path >> LO Out Power/LO In Power

Note - Using External Synthesizer:

If you are using the PXIe-5653 as a source to the Leader device, you need to connect its LO1 to LO2 port of the PXIe-5831 with 3dB attenuator, and set its LO1 to a supported value by the 5831. For this you can set your carrier frequency with the RFSG/RFSA driver then read the LO frequency property). Refer to below image for supported LO2 values with respect to the configured carrier:

Configure NI-TClk

To Configure NI TClk on generation and/or analyzer side, first you must obtain the session reference for each device including the Leader, then use TClk Synchronization APIs to configure the device for Homogeneous Triggers generation/analysis. Then enable TClk synchronization to align the triggers between the different devices and finally Initiate the generation/Acquisition where all devices start at the same trigger.

Note- This implementation of TClk is compatible with continuous acquisition/generation mode and does not support Start or Reference Trigger sharing.

Note - Synchronous Generation and Reception

The above cases synchronize multi-channel Tx paths or multi-channel Rx path. If you would like to synchronize the Tx and Rx paths together, then you need to consider the below modifications:

- Share the LO between the Tx and Rx paths by setting the LO Source property in RFSA/RFSG to SG SA Shared on the Leader Device instead of Onboard while maintaining LO_In on the Followers. The SG SA shared property internally shares the LO between both paths as described in the Overview section. Setting the LO source to LO_In on the Followers ensures that both Tx and Rx paths use the same external reference LO

- Include both RFSA and RFSG sessions in the list of devices wired to niTClkConfigure for Homogeneous Triggers VI. This ensures that the trigger alignment happens on all devices to initiate both generation and acquisition at the same trigger