Issue Details

I am using FAM NI 6583 together with NI PXIe-7976 . In my application, I am wiring directly

DDC_A_Strobe to the loop as a timing signal source (133MHz), basing on NI 6583 Channel CLIP configuration. When I start the target application, I receive the following error:

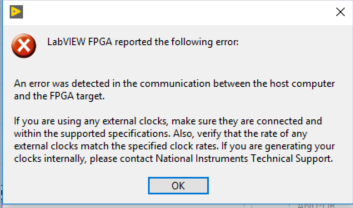

An error was detected in the communication between the host computer and the FPGA target.

If you are using any external clocks, make sure they are connected and within the supported specifications. Also verify that the rate of any external clocks match the specified clock rates. If you are generating your clocks internally, please contact National Instruments Technical Support.

I prepared other application just for measuring the frequency of the signal with given constant timing (310MHz). The test was successful, so it is not the fault of the clock itself.