Solution

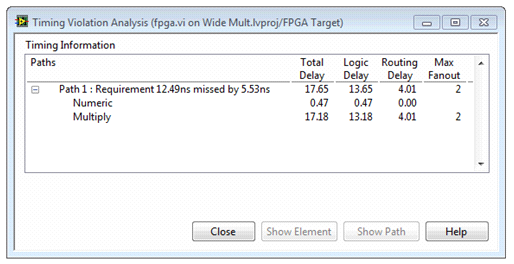

If you are receiving a timing violation from a multiplication function, the timing violation analysis window may look similar to that shown below.

These types of timing violations are often attributed to large input data types. 64-bit fixed-point inputs to a multiplication function are likely candidates to fail timing in clock domains of 40 MHz or higher. DSP blocks on the FPGAs in National Instruments hardware typically use 18-bit multipliers. In the event of a 64-bit multiplication, several 18-bit multipliers must be chained together to execute the arithmetic, yielding longer logic and routing delays. Other considerations that increase the likelihood of timing violations include:

- Coercion at input/output terminals - require extra time to execute to the data type conversion

- Faster clock domains - decrease the amount of time available to execute the function

- High resource utilization - fewer available DSP blocks tend to cause longer routing delays

There are several methods you can use to help reduce the likelihood of such timing violations.

- Lower the frequency of the top level FPGA clock

- Place the multiplication function inside a single cycle timed loop (SCTL)

- Use the smallest input data types that represent the data accurately

- Remove coercion by explicitly converting between data types

Timing violations of this nature can be generally avoided by using good programming practices in LabVIEW FPGA. For more information, please see

Best Practices for Development with the LabVIEW FPGA Module.