The module's reference can be used to access to each channel programatically using the

shared Variable pallete . To do this the following steps have to be implemented in the code:

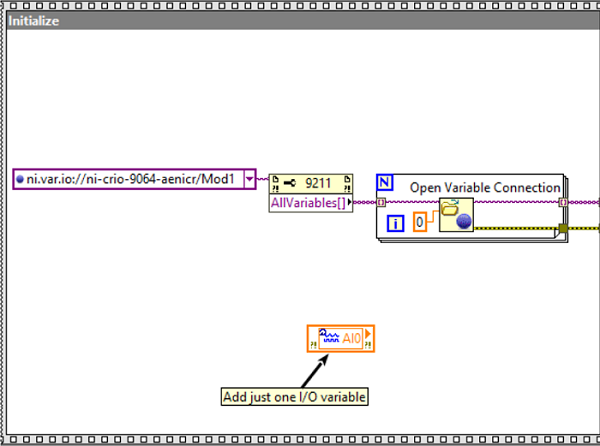

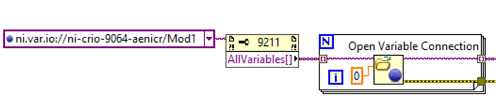

- Use the reference of the module and a property node to access the references of all the channels of the module. Then use a for loop with auto-indexing to open the reference of each variable using the Open Variable Connection Reference.vi.

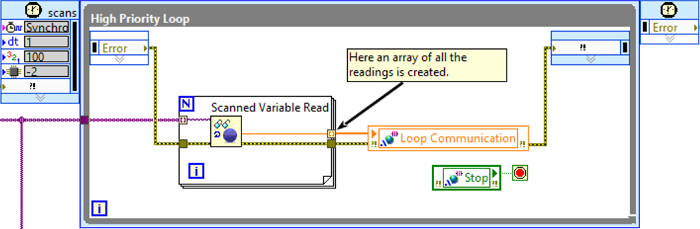

- To read the channel values, you can use a Timed Loop to scan all the variables. Each variable has to be scanned individually, so you must use a for loop. To scan each channel use the Scanned Variable Read.vi.

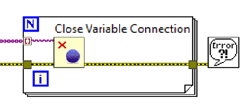

- When you have completed reading from the channels, all the channel references have to be closed using the Close Variable Connection.vi.

For a possible implementation, please refer to a LabVIEW example by going to

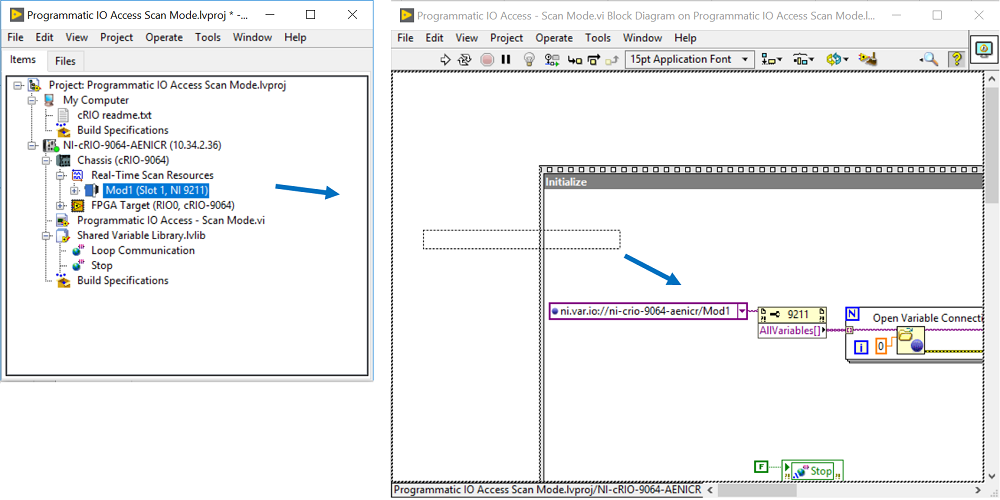

Help>>Find Examples>>Browse>>Hardware Input and Output>>CompactRIO>>NI Scan Engine>>Advance>>Programmatic IO Access-Scan Mode.lvproj.

Additional Information

Adding the module reference to the block diagram.

To add the reference of the module to the block diagram simply pick the module on the

project explorer and drag it to the code.

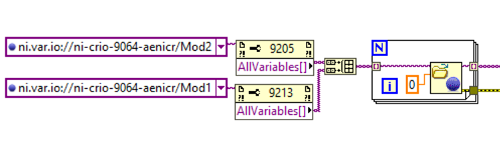

Adding references for more than one module.

More than one module can be added just dragging them and building an array with all the references.

Configuring the FPGA

When the LabVIEW project is created the FPGA has not been configured to route the physical channels of the modules we are using as I/O resources. In other words, the FPGA is not aware of the modules we are using. For that reason, if we just create a project with and try to run it the application will not provide channel readings from the modules. There are two ways to configure the FPGA.

- Create a blank VI on the FPGA and compile it. This will create a bit file that is intended to configure all the I/O blocks to link them to the modules used on the cRIO.

- Add one I/O variable of any channel at the initialize section of the code. This will implement the scan mode predefined bit fil, which already set the configuration of the hardware used on the FPGA chip.