Issue Details

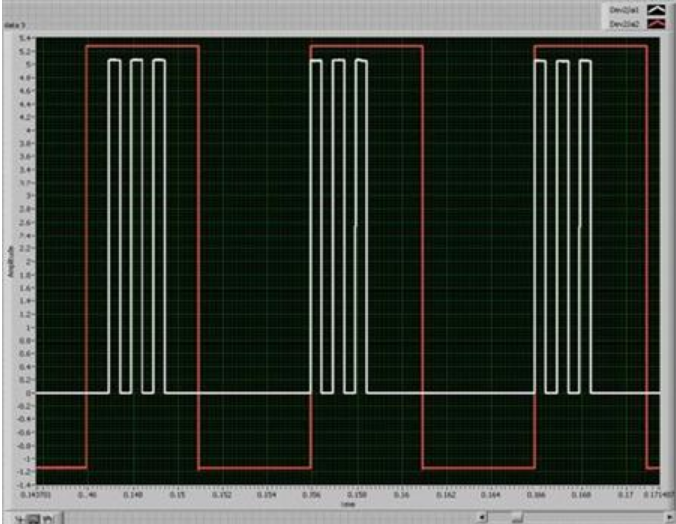

I want to generate a delayed, retriggerable, finite pulse train. When I generate a pulse train of one pulse, I get the expected behavior. The figure below shows this behavior with a delayed retriggerable single pulse 1kHz pulse train + 1ms initial delay.

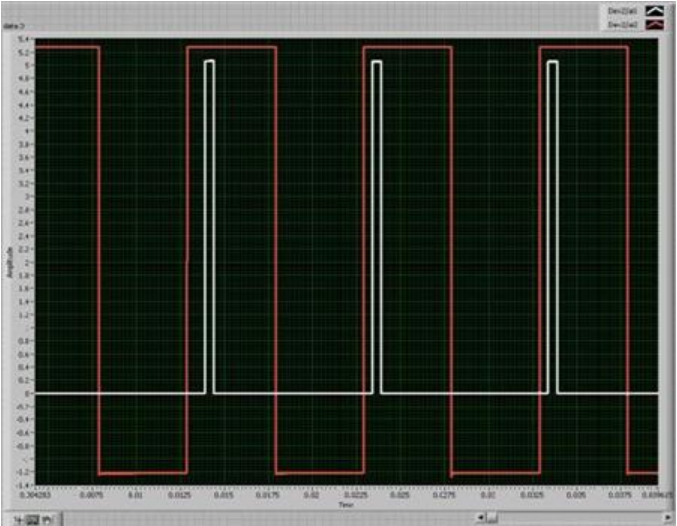

When I try to do a delayed, retriggerable finite pulse train generation, the delay occurs properly only at the first trigger but not at the others. The second figure below demonstrates this behavior with a delayed retriggerable pulse train at 1kHz + 1ms initial delay. For later triggers, the counter acts immediately and the finite pulse train is triggered with no delay even when the Low Time is set. How can I correct this?