Solution

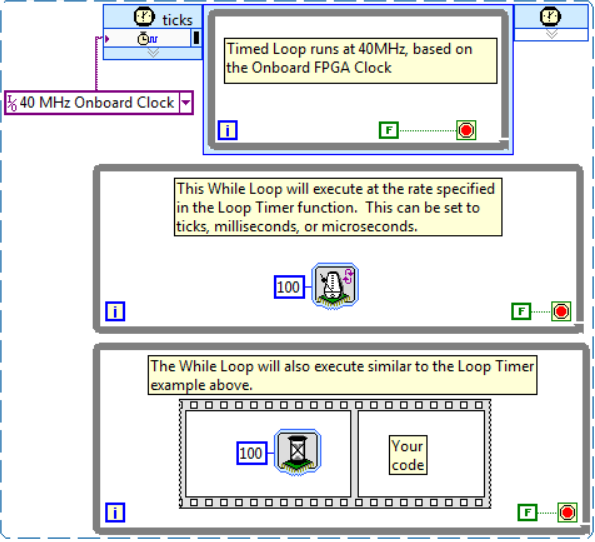

On an FPGA Target, the Timed Loop structure can only run as a single cycle Timed Loop. The only parameter that matters is the Source Name. The Source Name defaults to the 40MHz FPGA clock, but can be configured to use a derived clock. The compiler ignores every other parameter.

If you want to implement other custom timing options, you can use a While Loop with either a Loop Timer, Wait function, or Sequence structure. Examples of these implementations are shown below, and can also be seen in the FPGA Module Help in the Related Links section.