Solution

Depending on the degree to which you want to reduce power consumption, there are different ways you can reduce the power your cRIO consumes.

- The primary way to reduce power consumption on a cRIO is to enable Sleep Mode.

Sleep Mode is enabled by calling the Sleep channel on the FPGA. The Sleep channel can either be accessed by placing an FPGA I/O Node on the FPGA Block Diagram or by simply dragging the Chassis I/O Item from the Project Explorer to your block diagram as shown below.

cRIO 90xx models with embedded FPGA targets all have sleep lines that you can write to to set your modules into sleep mode. In sleep mode, the system consumes minimal power and may dissipate less heat than it does in normal mode. Typically, you cannot communicate with modules when they are in sleep mode. If you try to communicate with a module when it is in sleep mode, LabVIEW returns a module communications error from the FPGA I/O functions. Sleep mode does not affect the CompactRIO chassis or controller, so the FPGA and any Real-Time code will continue to run. You cannot write to the Sleep channel if you are using the Scan Interface with any modules in the system.

- If you need to further reduce power consumption, you can shut down the controller's Real-Time OS.

You can shut down the controller's RTOS by manually powering down the system, or by using console commands to shut down the Linux RTOS. You can call these console commands programmatically using

these methods, using either the

Call Library Function Node or the

System Exec VI.

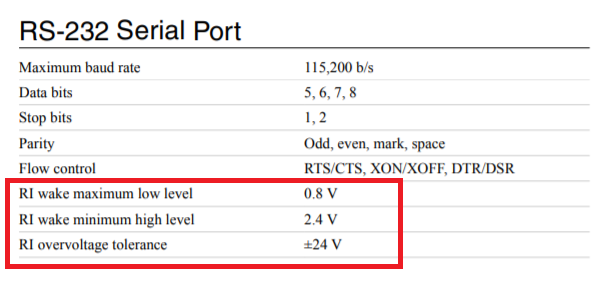

If you have a device with a Ring Indicator line on its serial port, like the cRIO 903x and 904x, you can wake your device and restart it's RTOS using this line. Otherwise, you will need to manually power the device back on.

Note:

Note: If you power your device's OS off using this method, any code you have running on the device's RTOS will stop running. This is generally only recommended for situations where your device will not be actively collecting/processing data, or where all aspects of the device's operation are isolated to the FPGA.