Solution

All of the FPGA timing functions are based on the same internal counting device in the RIO hardware; however, they do not all have the same start time for the tick counts. With the limited size of an FPGA chip, resource usage is something you should always be looking to trim down where possible. When using multiple timing functions in the same VI, it is important to understand how they function in unison and which ones can and cannot be used together. The FPGA timing functions are shown below.

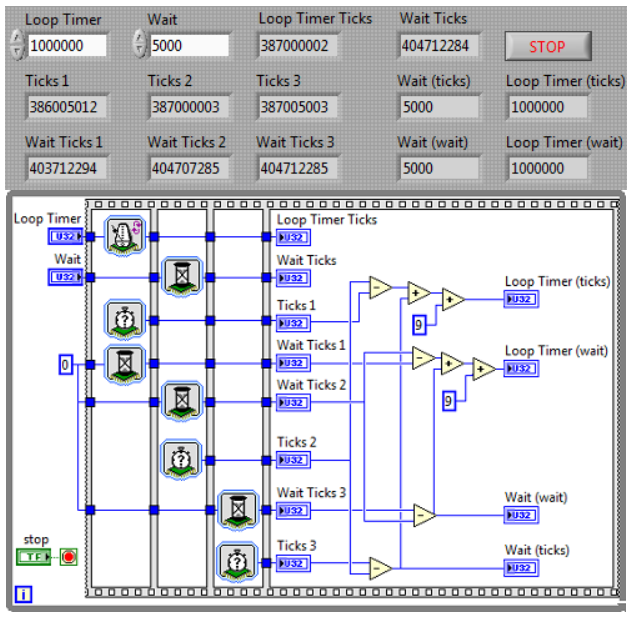

Using the Tick Count and Loop Timer:

Using the Tick Count and Loop Timer:The Tick Count and Loop Timer functions use the same start time, while the Wait functions use a different start time. Because of this, you cannot reliably benchmark code using these functions together. See the VI below for an example of this. If you plan to use a Wait function, you should use only Wait functions and give them an input of zero. This gives the same functionality as the Tick Count VI.

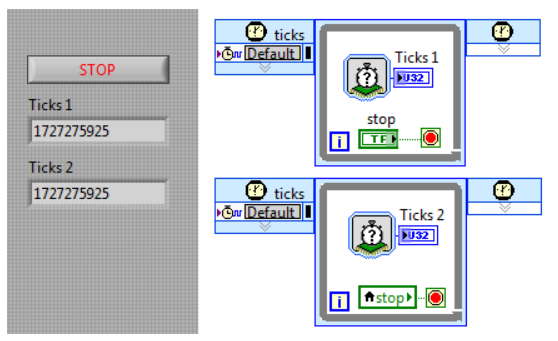

Using Tick Count VIs in different loops:

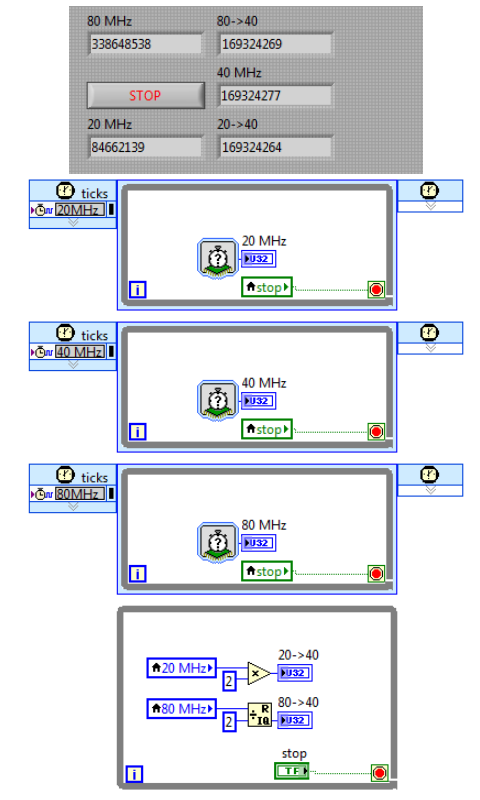

Using Tick Count VIs in different loops:You can also use the Tick Count VIs inside single-cycle timed loops. Each Tick Count VI will start at the same time and count at the rate of the loop. If the loops are running at the same rate, the tick counts will be synchronized. If the loops are running at different rates, you can use scaling functions to make the values comparable, but they may not be exactly synchronized. This is because the scaling functions cannot always execute inside the loop due to single-cycle timing, and using scaling functions in a separate loop will lead to race conditions which will cause the values to be slightly off. An example of loops running at the same rate and different rates are shown below.

Same rate - timing synchronized:

Different rates - timing not synchronized: