Solution

User-Controlled I/O Sampling is an advanced LabVIEW FPGA interface that allows user to have greater control over sampling operations. The primary benefit is that modules that support this interface can run at a higher sample rate than with the I/O Node.

Not all modules support User-Controlled I/O Sampling. For supported modules, check the module datasheet (FPGA user-controlled I/O sampling specification) or the CompactRIO Device Drivers help documentation.

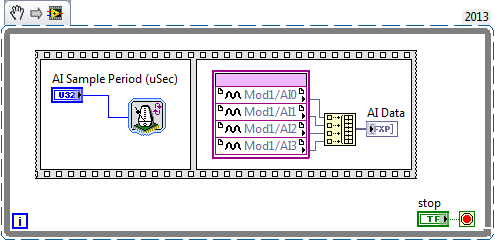

Typical I/O Node operation:

In a typical I/O Node, operations happen serially. When the I/O Node is called, the node tells the module to acquire data and then transfers the data from the module. The I/O Node cannot be called again until both operations are complete, so the acquisition rate is determined by the time it takes the module to acquire the data and transfer the data back to the FPGA.

For example, with the NI 9222 and NI 9223 the maximum sample rate an I/O Node is 300 kS/s and 350 kS/s respectively.

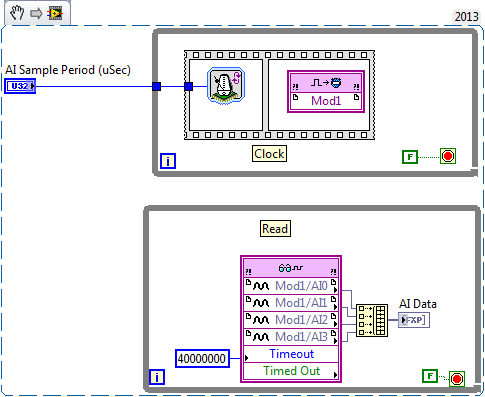

Typical User-Controlled I/O Sampling operation:

With User-Controlled I/O Sampling, operations can happen in parallel. The Clock node controls when the module acquires data, the Read node controls when data is transferred. Since these are separate operations the Clock node can run while the data is transferring from the module. The sample rate is now determined by the time it takes for the module to have the data ready for transfer. For example, with the NI 9222 and NI 9223 the maximum sample rate with the User-Controlled I/O Sampling is 500 kS/s and 1 MS/s respectively.