해결책

이 문제는 LabVIEW FPGA 2010에서 사용하는 Xilinx ISE 컴파일러의 버그로 인해 발생합니다. 이 문제가 발생하면 여러 어댑터 모듈 CLIP 항목에 필요한 IODelayCtrl 구성 요소를 배치하는 데 사용 된 알고리즘이 실패 할 수 있습니다.

소프트웨어 업데이트 설치 :

- 컴퓨터에서 실행중인 LabVIEW 및 모든 컴파일 작업자를 닫습니다.

첨부 파일 <patch.zip>을 다운로드 하십시오. - 이 파일을 압춥을 해제하고 프로그램 디렉토리를 NI FPGA 파일 디렉토리에 복사하십시오. 이 디렉토리는 Windows XP 및 Windows 7의 경우 C:\NI FPGA 경로에 있습니다.

- 충돌하는 파일을 바꾸려면 예를 클릭하십시오. Xilinx ISE 설치 디렉토리의 영향을 받는 파일이 대체됩니다.

- 내 컴퓨터를 마우스 오른쪽 버튼으로 클릭하고 속성을 선택하십시오.

- Windows 7의 경우 고급 시스템 설정(Advanced system settings)을 클릭하십시오.

- 고급 탭으로 이동하십시오.

- 환경 변수...(Environment Variables...)를 클릭하십시오.

- 시스템 변수 범주에서 새로 작성...(New...)을 클릭하여 새 환경 변수를 작성하십시오.

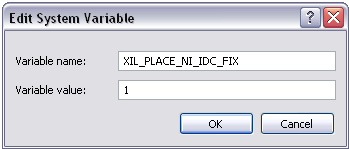

- 변수 이름으로 XIL_PLACE_NI_IDC_FIX를 입력하십시오.

- 변수 값 1을 입력하십시오. 다음 이미지를 참조하십시오.

11.

확인을 클릭하여 환경 변수를 작성하십시오.

확인을 클릭하여 환경 변수 창을 종료하십시오.

확인을 클릭하여 시스템 등록 정보 창을 종료하십시오.

12. 변수를 적용하려면 컴퓨터를 다시 시작하십시오. 참고로이 문제로 인해 다음 오류 중 하나가 발생할 수 있습니다.

오류 예시 1 :경우에 따라 Xilinx ISE 컴파일러가 컴파일의 맵 단계에서 충돌 할 수 있습니다. 이 상황에서 Windows 또는 Visual Studio JIT 디버거는 Map.exe 프로세스가 실패했음을 나타내는 오류를 반환합니다.

LabVIEW는 또한 다음과 유사한 에러를 반환합니다 :

Compilation failed due to a Xilinx error.

Details:

ERROR:TclTasksC:process_077: Failed to complete. Please inspect the log and report files.false

while executing

"process run "Generate Post-Map Static Timing""

(file "C:\NIFPGA\jobs\entb5e7_V5WxwWH\mapTrce.tcl" line 8)

ERROR: Mapped NCD file "Puma20Top_map.ncd" not found.

Please run the "Map Report" process first to generate the mapped NCD file.

or right click on the "Pre-Route Static Timing Report" process and select 'Rerun All'.

오류 예시 2 :

Xilinx ISE 컴파일러는 필요한 IODelayCtrl 구성 요소가 설계에서 누락되었다고보고 할 수 있습니다. 이 경우 다음과 유사한 에러가 LabVIEW 컴파일 요약 창에 나타납니다 :

Compilation failed due to a Xilinx error.

Details:

ERROR:TclTasks C:process_077: Failed to complete. Please inspect the log and report files.false

while executing

"process run "Map""

(file "C:\NIFPGA\jobs\MP5f213_KI40c7b\map.tcl" line 8)

ERROR:PhysDesignRules:1613 - IDELAYCTRL not found for clock region CLOCKREGION_X0Y4. The IODELAY block

Puma20Window/theCLIPs/IO_Module_CLIP0/Ni5761Topx/Ni5761AdcSamplerx/Ni5761CaptureAdcx/Data01Capture/GenMasterMonitor[3].MasterIdelay has an IDELAY_TYPE attribute of either FIXED or VARIABLE. This programming requires that there be an IDELAYCTRL block programmed within the same clock region.

이 패치 설치중 문제가 발생하는 경우 National Instruments에 문의 하시기 바랍니다.