Solution

This issue is caused by a bug in the Xilinx ISE compiler used by LabVIEW FPGA 2010. When this issue is present, the algorithms used to place IODelayCtrl components required by several adapter module CLIP items may fail.

Install Software Updates :

- Close LabVIEW and any compile workers running on your computer.

Download the attached file <patch.zip>. - Extract the contents of this file and copy the programs directory into the NI FPGA files directory on disk. This directory is located at C:\NI FPGA for Windows XP and Windows 7.

- Click Yes to replace any conflicting files. This will replace the affected files in the Xilinx ISE install directory.

- Right click on My Computer and select Properties.

- For Windows 7, click advanced system settings.

- Navigate to the Advanced tab.

- Click Environment Variables.

- In the System variables category, click New to create a new environment variable

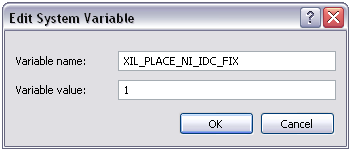

- Enter XIL_PLACE_NI_IDC_FIX as the variable name.

- Enter a variable value of 1. Use the following image for reference

11. Click OK to create the environment variable. Click OK to exit the Environment Variables window.

Click OK to exit the System Properties window.

12. Restart your computer to allow the variable to take effect For reference, this issue may cause one of the following errors:

Example Error 1:In some cases, the Xilinx ISE compiler can crash during the Map stage of the compilation. In this situation, Windows, or the Visual Studio Just-In-time Debugger, returns an error indicating that the Map.exe process has failed.

LabVIEW also returns an error similar to the following:

Compilation failed due to a Xilinx error.

Details:

ERROR:TclTasksC:process_077: Failed to complete. Please inspect the log and report files.false

while executing

"process run "Generate Post-Map Static Timing""

(file "C:\NIFPGA\jobs\entb5e7_V5WxwWH\mapTrce.tcl" line 8)

ERROR: Mapped NCD file "Puma20Top_map.ncd" not found.

Please run the "Map Report" process first to generate the mapped NCD file.

or right click on the "Pre-Route Static Timing Report" process and select 'Rerun All'.

Example Error 2:

The Xilinx ISE compiler could report that required IODelayCtrl components are missing from the design. In this case, an error similar to the following appears in LabVIEW Compile Summary Window:

Compilation failed due to a Xilinx error.

Details:

ERROR:TclTasks C:process_077: Failed to complete. Please inspect the log and report files.false

while executing

"process run "Map""

(file "C:\NIFPGA\jobs\MP5f213_KI40c7b\map.tcl" line 8)

ERROR:PhysDesignRules:1613 - IDELAYCTRL not found for clock region CLOCKREGION_X0Y4. The IODELAY block

Puma20Window/theCLIPs/IO_Module_CLIP0/Ni5761Topx/Ni5761AdcSamplerx/Ni5761CaptureAdcx/Data01Capture/GenMasterMonitor[3].MasterIdelay has an IDELAY_TYPE attribute of either FIXED or VARIABLE. This programming requires that there be an IDELAYCTRL block programmed within the same clock region.

Contact National Instruments support if you have any issues installing this patch.