Solution

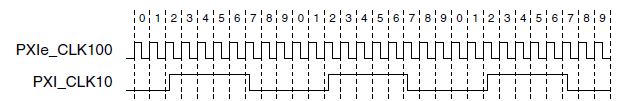

PXI_CLK10 is generated from PXIe_CLK100. They are phase lock looped (PLL) together. The PXI_CLK10 and PXIe_CLK100 have the following default timing relationship:

As shown in the above default timing relationship, there may be up to 6.5 ns of skew between PXI_Clk10 and PXIe_Clk100. However, this delay is constant due to PXI_Clk10 and PXIe_Clk100 being PLL together so you can synchronize all modules in your PXIe chassis. For more information on using reference clock synchronization please see the White Paper article

Synchronization Explained .