以下の解決策を試す前に、DAQmx関数の経験(DAQmxコースで習得)があることをお勧めします。すべてのソリューションは、DAQmx APIを使用してハードウェアを同期します。

DAQ コースとその内容の詳細については、このリンクを参照してください。

さまざまなタイプの同期

シャーシ間の同期は、次のようなさまざまなセットアップを参照できます。

- PXI(e)の外部BNCコネクタを使用してクロックを出力する

- 異なるシャーシの2つのデータセットを1つのファイルにまとめる

- トリガーを共有することで、2台のシャーシでDAQを同時に開始

- 基準クロックまたはマスター タイムベースの共有

上記はすべて同期の形式であり、さまざまなレベルの精度を提供します。特定のハードウェアを必要とする方法もあれば、2つのPXI(e)シャーシのみを必要とする方法もあります。いくつかの設定を組み合わせることで、可能な限り最高レベルの精度と確定性が得られます。

PXI_CLK10 OUTをPXI_CLK10 INに接続する - BNCコネクタ

このレベルの同期は、ハードウェアモジュールを必要としないため、比較的簡単に実現できます。 2つのシャーシを使用している場合、1つのシャーシのマスターのPXI_CLK10 OUTを別のシャーシのPXI_CLK10 INに接続できます。これにより、両方のPXI(e)に共通のタイムベースが共有され、ドリフトが防止されます。この方法は、2つのPXIeシャーシ、2つの PXIシャーシ、および PXIe/PXIの組み合わせに対して実行できます。

BNC コネクタを使用すると、クロックが存在する場合、自動的にPXIシステムクロックが上書きされます。これにより、2つのクロック波形間に非常に小さな時間スキューが発生します。これは、2つのPXIシステム間では無視できますが、シャーシをデイジーチェーン接続すると増加します。このスキューを大幅に削減するには、各PXI_CLK10 INコネクタに接続する等長ケーブルを備えた外部10 MHzクロックソースを使用します。

この方法は、システムを低度に同期します。より高い同期を実現するには、タイミングおよび同期ハードウェアモジュールを使用する必要があります。

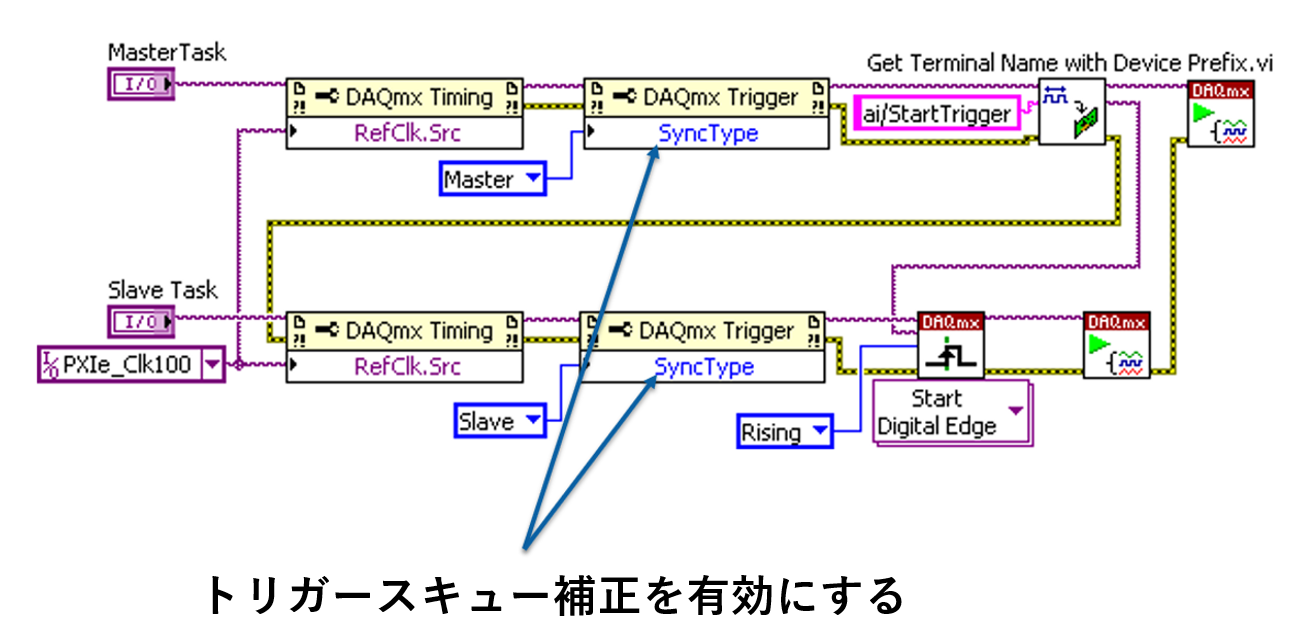

トリガー共有 - タイミングと同期 (T&S) モジュールが必要

トリガー共有により、両方のシャーシがほぼ同時にDAQを開始することが保証されます。システム内の各PXI(e)には、各PXI(e)間でトリガラインを共有するT&Sモジュールが必要です。以下に示すブロックダイアグラムの例は、トリガーラインを一緒に同期する方法を示しています。

ここでは、トリガーソースがマスタータスクで定義され(コードの一番上の行)、スレーブタスクに送信されます(コードの一番下の行)。トリガーが検出されると、スレーブタスクが開始され、続いてマスタータスクが開始されます。この順序は必須であり、スレーブは常にマスターより前に開始する必要があります。 1つのタスクが次々と開始されることによって生じるスキューを修正するために、DAQmxトリガープロパティノードを使用して、1つのチャンネルをマスターとして、もう 1つをスレーブとして定義します。

この同期方法を前の例と組み合わせると、スキューやドリフトのないシステムが作成されます。ただし、両方のシャーシが同じ速度で動作する必要があります。

基準クロックの共有

基準クロックは、他のシステムのクロックによって参照され、独自のクロック信号を導出するクロック信号です。このクロックをデバイス間で共有すると、ドリフトとスキューを最小限に抑えながら、各シャーシを異なるレートで実行できます。基準クロックを共有するにはT&Sモジュールが必要で、前の図に示すように実装できます (同じソースでDAQmxタイミング プロパティノードを使用することにより)。

基準クロックを共有することの欠点の1つは、高周波アプリケーションの場合、クロック信号が5 ~ 10 MHz付近の周波数で劣化し始めることです (外部クロック ソースとボード間の配線に使用されるケーブルによって異なります)。さらに、信号パスの長さに応じて、高速で顕著な位相遅延を導入する伝送遅延があります。

すべてのタイミング ソースはシステムにジッターを導入し、ボードを同期しようとすると重大になる可能性があります。開始トリガを使用して測定システム内のすべてのボードで同時に収集を開始する場合、通常、各ボードは開始トリガを受信するとボードクロックの 1 ~ 2 チック以内にトリガし、ボード間に位相遅延が生じます。

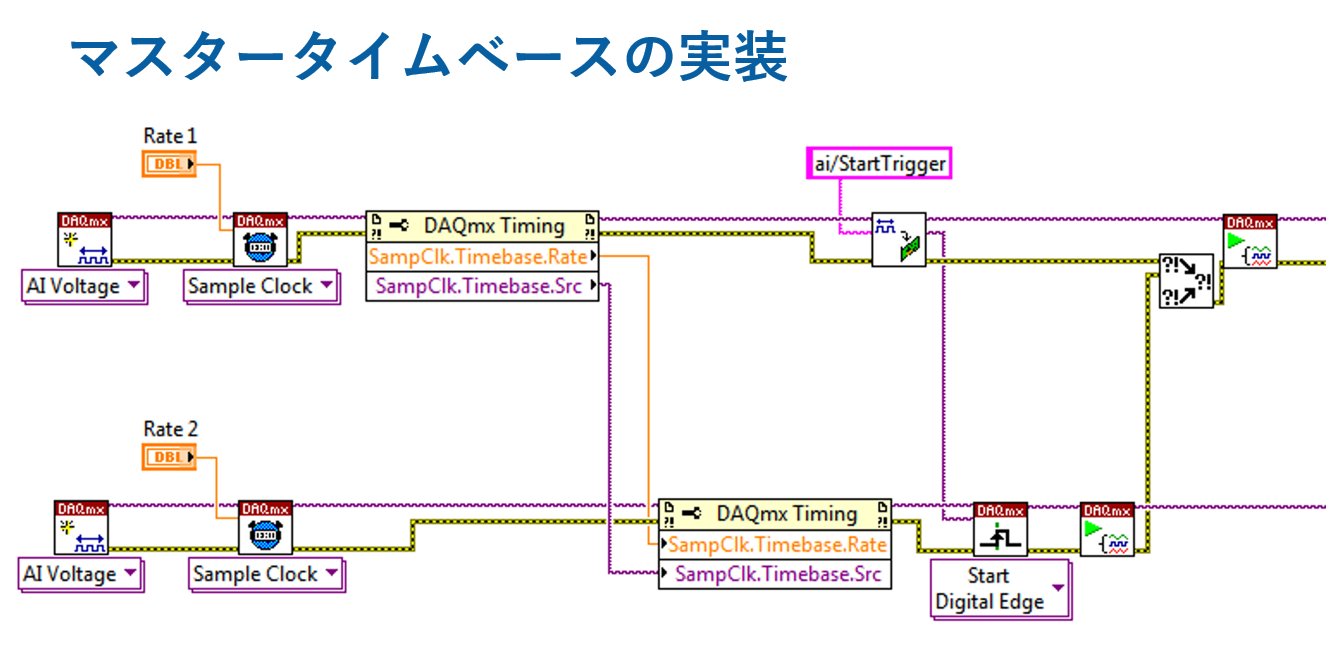

マスタータイムベースの共有

マスタータイムベースを共有すると、基準クロックを共有する利点がすべて得られると同時に、ドリフトが解消されます。以下に示すように、プロパティノードを使用して共有されます。スレーブのクロックはマスターのクロックによって上書きされます。これは、すべてのハードウェアタイミングシステムが自動的にマスターシャーシと同期することを意味します。タイムベース共有の性質上、このシステムは不安定になる可能性があるため、使用前にシステムが安定していることを確認してください。

追加情報

可能な限り最高レベルの同期を達成する

最高レベルの同期を実現するには、システムに何らかの形式のクロックとトリガーの共有を含めます。この良い例は、T&Sモジュールを使用してPXI(e)間で基準クロックとトリガを共有することです。