In order to determine the maximum frequency of the Primary Control Loop and Model Loop you can increase the Target Rate until the LP Count, HP Count, and Model Count System Channels become equal to zero and stay constant.

You can use the

NI VeriStand Benchmark Tool to automate increasing Target Rate and verify that LP Count, HP Count, and Model Count System Channels equal zero. The instructions for determining a maximum PCL Rate for the model are the following:

- Download and unzip the utility from the NI VeriStand Benchmark Tool page.

- Launch the NIVS Benchmarker.exe application.

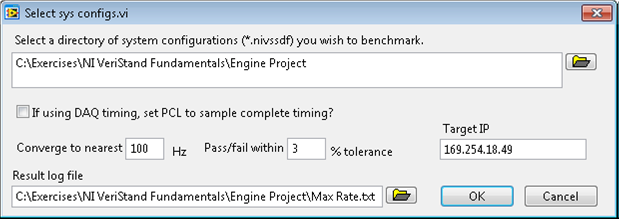

- Configure corresponding parameters in Select sys configs dialog window:

- Select a directory with .nivssdf files, that you are going to test. Each of the selected System Definition files will be tested to estimate its maximum PCL Rate.

- Set the desired PCL Rate to Converge to nearest control box.

- Set the Target IP of your controller.

- Choose a Result log file to save the test result.

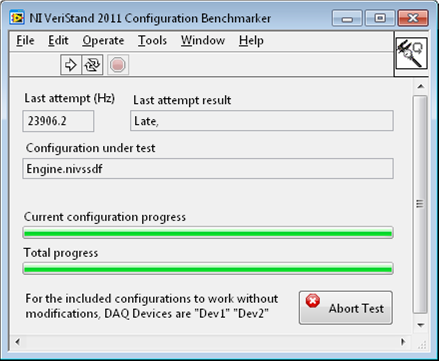

- Click OK. The NI VeriStand Configuration Benchmarker window will appear, and the System Definition files will continuously deploy at different PCL frequencies until the maximum frequency at which the System Channels Counters (HP, LP, and Model Counts) will become equal to zero.

- Open Max Rate.txt and find the Maximum PCL Rate in Hz for every System Definition file.