解決方案

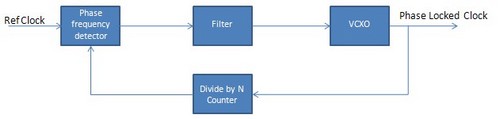

一個鎖相環(PLL)是一個設計用於同步板子時脈與外部的時脈訊號的電路。鎖相環電路會比較外部訊號與電壓控制的石英震盪器(VCXO)之間的相位,接著會去修正震盪器的時脈訊號去與參考訊號的相位之間吻合。因此,訊號之間將會精密的同相。

當在處理訊號擷取時,由於鎖相環會使得多個裝置共享一個參考訊號,是相當有用的同步技術。也因此裝置之間能夠同步80MHz或是20MHz甚至是特定裝置上的取樣時脈。由於各個取樣時脈之間的同步,每個裝置也能夠精密的在特定時間同時取樣。

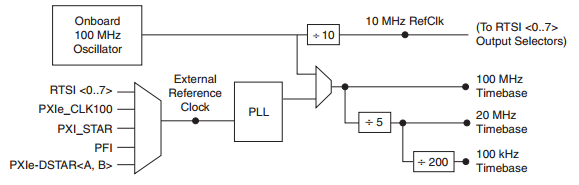

下圖說明了關於鎖相環的運作機制,可於M系列的使用手冊上取得。

圖1. M系列時脈

圖1. M系列時脈這個方塊圖說明了M系列DAQ裝置是如何利用鎖相環去得到時脈訊號。

圖2顯示了M系列DAQ裝置上使用的PLL框圖。

圖2. PLL框圖

圖2. PLL框圖

實際上在程式撰寫中對多個裝置同步取樣時脈時,會需要根據實際硬體的類別而定。以PCI介面的產品來說(M系列PCI DAQ,PCI Digitizer…等)所有的同步則是透過RTSI時脈與觸發去共享訊號。在這樣的情況下,會有一個裝置需要作為Master且透過RTSI去分享內部時脈給Slave裝置們。原則上,PXI介面的產品也能與PCI的做法一樣去實現同步。但是,使用PXI介面,鎖相環的同步方式更常用於將裝置與PXI機箱背板上的10MHz時脈同步,這些背板時脈則是透過PXI trigger去分享的。關於每個儀器對於鎖相環的規範,請參考以下相關連結。