해결책

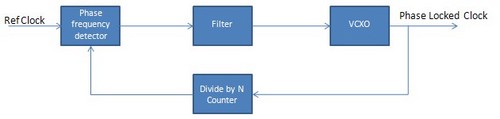

위상 고정 루프 (PLL)는 한 회로 기판이 온보드 클럭의 위상을 외부 타이밍 신호와 동기화 할 수 있도록 설계된 피드백 회로입니다. PLL 회로는 외부 신호의 위상을 전압 제어 크리스털 발진기(VCXO)에 의해 생성된 클럭 신호의 위상과 비교하여 작동합니다. 회로는 발진기의 클럭 신호의 위상을 조정하여 기준 신호의 위상과 일치시킵니다. 따라서, 원래의 기준 신호와 새로운 신호는 서로 정확하게 동 위상이 됩니다.

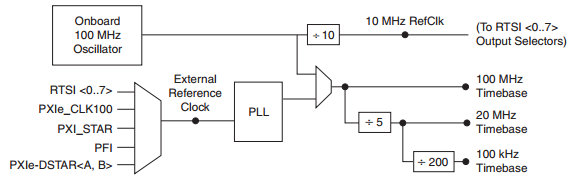

이것에 대한 좋은 예가

DAQ X Series User Manual 에서 참조한 다음

그림 1에 나와 있습니다.

그림 1.

그림 1. X 시리즈 타이밍 소스

이 블록 다이어그램은 X 시리즈 DAQ 디바이스에서 나머지 타이밍 신호를 파생시키기 위해 PLL을 사용하는 방법을 보여줍니다.

그림 2 는 M 시리즈 DAQ 디바이스에서 사용되는 PLL의 블록 다이어그램입니다.

그림 2.

그림 2. PLL 블록 다이어그램

위상 고정 루프를 통해 여러 보드의 샘플 클럭을 동기화하는 데 필요한 실제 프로그래밍 기술은 사용중인 하드웨어 유형에 따라 다릅니다. PCI 기반 제품 (X 시리즈 PCI DAQ, PCI 디지타이저 등)의 경우 RTSI (Real Time System Integration) 타이밍 및 RTSI 케이블로 연결된 트리거 라인을 통해 신호를 공유함으로써 모든 동기화가 수행됩니다. 이 시나리오에서는 하나의 보드가 마스터로 작동하고 RTSI 라인을 통해 마스터의 내부 클럭을 슬레이브 보드들에 내보냅니다.

PXI 기반 제품을 사용하면 PCI 카드와 동일한 방법을 적용 할 수 있지만, PLL 동기화는 섀시의 백플레인에 내장 된 PXI 섀시 10MHz 클럭과 각 보드의 클럭을 동기화하여 수행하는 것이 더 일반적입니다. PXI 트리거 라인을 통해 액세스 할 수 있습니다. 위상 고정 루프에 대한 장비 별 정보는 아래 링크를 참조하십시오.