Solución

- Bucle de bloqueo de fase (PLL)

Un bucle de bloqueo de fase (PLL) es un circuito de retroalimentación diseñado para permitir que una placa de circuito sincronice la fase de su reloj integrado con una señal de temporización externa. Los circuitos PLL funcionan comparando la fase de una señal externa con la fase de una señal de reloj producida por un oscilador de cristal controlado por voltaje (VCXO). Luego, el circuito ajusta la fase de la señal de reloj del oscilador para que coincida con la fase de la señal de referencia. Así, la señal de referencia original y la nueva señal están precisamente en fase entre sí.

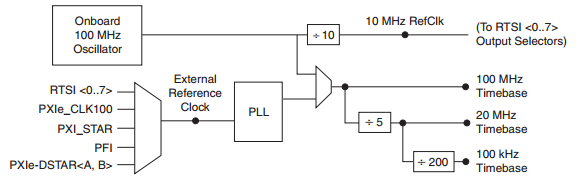

Un buen ejemplo visual de esto se muestra en la siguiente

figura 1 del

manual de la Serie X.

Figura 1.

Figura 1. Fuentes de temporización de la serie X

Este diagrama de bloques muestra cómo se utiliza el PLL para derivar el resto de las señales de temporización en los dispositivos DAQ de la serie X.

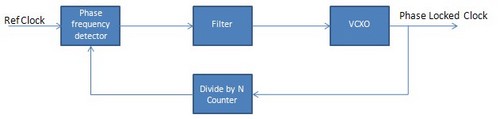

La Figura 2 muestra un diagrama de bloques del PLL que se utiliza en los dispositivos DAQ de la Serie M.

Figura 2.

Figura 2. Diagrama de bloques de PLL

Las técnicas de programación reales necesarias para sincronizar los relojes de muestra de varias placas a través de un bucle de bloqueo de fase dependen del tipo de hardware en uso. Con los productos basados en PCI (placas PCI DAQ de la serie X, digitalizadores PCI, etc.), toda la sincronización se realiza compartiendo señales a través de líneas de activación y temporización de Integración de sistemas en tiempo real (RTSI) conectadas mediante un cable RTSI. En este escenario, una placa funcionará como maestra y exportará su reloj interno a través de una línea RTSI a las placas esclavas.

Con los productos basados en PXI, se puede aplicar el mismo método que se utiliza con las tarjetas PCI; sin embargo, la sincronización PLL se realiza más comúnmente sincronizando el reloj de cada placa con el reloj del chasis PXI de 10 MHz, que está integrado en la placa posterior del chasis y accesible a través de las líneas PXI Trigger. Para obtener información específica del instrumento sobre el bucle de bloqueo de fase, consulte los enlaces a continuación.